Table of Contents

项目介绍

- 本项目目的是从头到尾演示一个小的FPGA项目的实现,供大家学习和提升自己。本项目涉及QT上位机开发、FPGA逻辑开发,对上位机不感兴趣的朋友可以忽略这部分,不影响FPGA部分的学习。

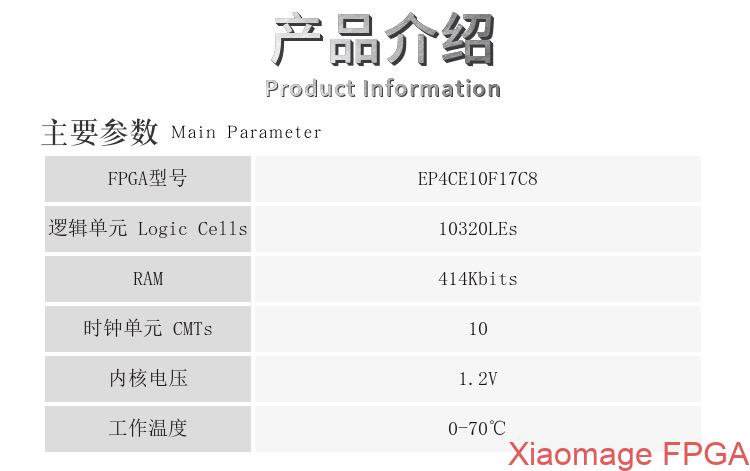

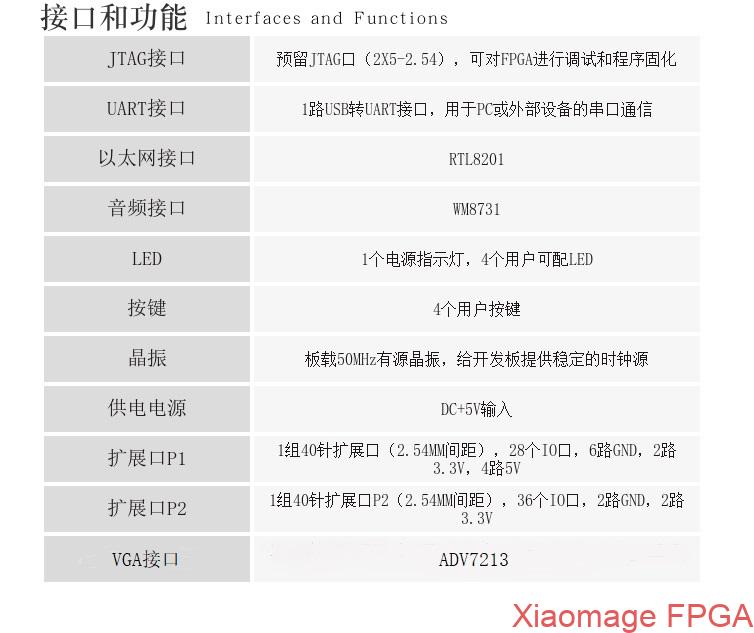

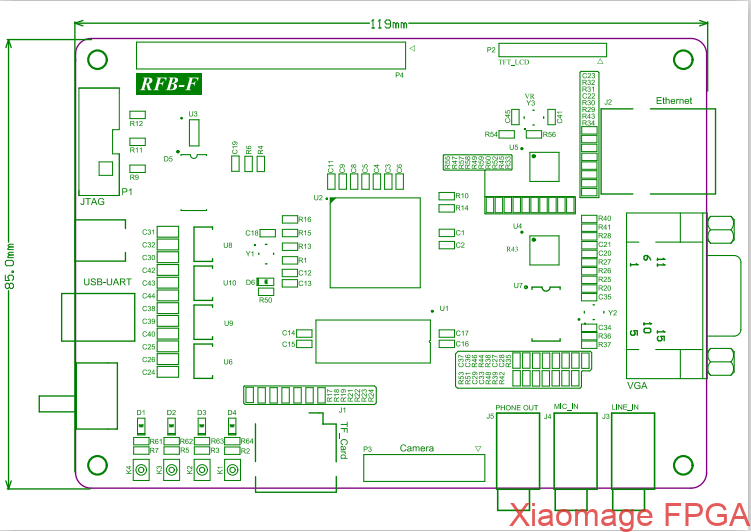

- 使用的硬件平台是DMK-301型FPGA开发板,该平台的资源参数如图所示:

- 软件平台:

-

- Quartusii18.1(下载、安装和破解教程)

- QT5.3+OpenCV3.0 链接:https://pan.baidu.com/s/1EEgRw-9M1fwS7iFZ1eR69Q 提取码:9cav 备选:http://gofile.me/48SuV/8dx71AR1Q(页面打开较慢,耐心等...)

功能定义

上位机打开一幅图片并将分辨率调整为640*480,并通过串口将彩色图像数据发送给FPGA,FPGA接收到上位机发来的数据后可以自动解析出图像数据,并将图像送给VGA显示屏显示。

详细要求

- 上位机可以通过“浏览”打开图片,图片格式支持BMP、JPG格式;

- 上位机可以自动调整图片的分辨率为640*480;

- 上位机通过串口发送图片的图像数据给FPGA,要求图像数据颜色空间为24bits全彩,即RGB888格式;

- FPGA接收到上位机传输来的数据,自动解析图像有效数据,并显示到VGA显示屏上,显示分辨率为640*480;

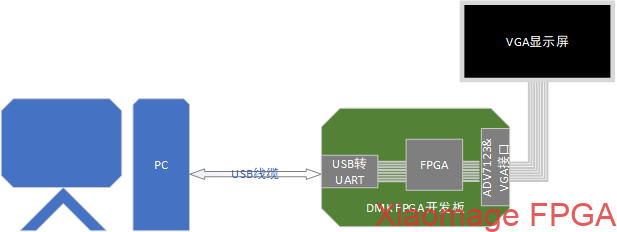

系统框图

整个系统由PC机、DMK301 FPGA开发板和VGA显示屏组成,其中PC和开发板之间使用Mini USB2.0线连接,FPGA和VGA显示屏之间通过VGA线连接。FPGA板上有一颗USB转UART芯片,可以使得PC和FPGA之间以UART协议进行通讯。

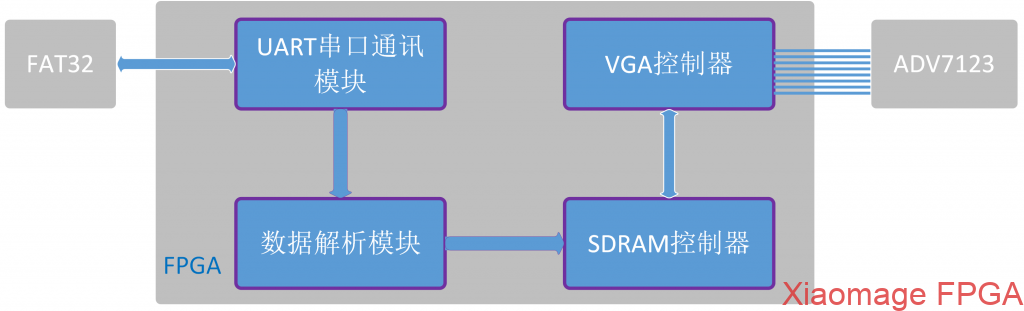

软件模块框图

- UART串口通讯模块:实现UART串口通讯功能,将串行数据转化成并行数据,以字节为单位输出数据;

- 数据解析模块:从字节数据流中提取并组合出有效的图像数据,并以RGB565格式存储到SDRAM控制器中;

- SDRAM控制器:SDRAM控制器模块,将负责的SDRAM读写操作封装成便于用户使用的用户接口,这是一种类似fifo的读写接口;

- VGA控制器模块:通过和SDRAM控制器模块交互来获取SDRAM中的图像数据,并产生符合VGA标准的视频时序输出图像给ADV7123。

调试记录

概率性传输数据错误

问题描述:串口传输图像数据过程中,概率性出现约SDRAM突发长度的像素数据不对

解决办法:添加时序约束

功能效果演示

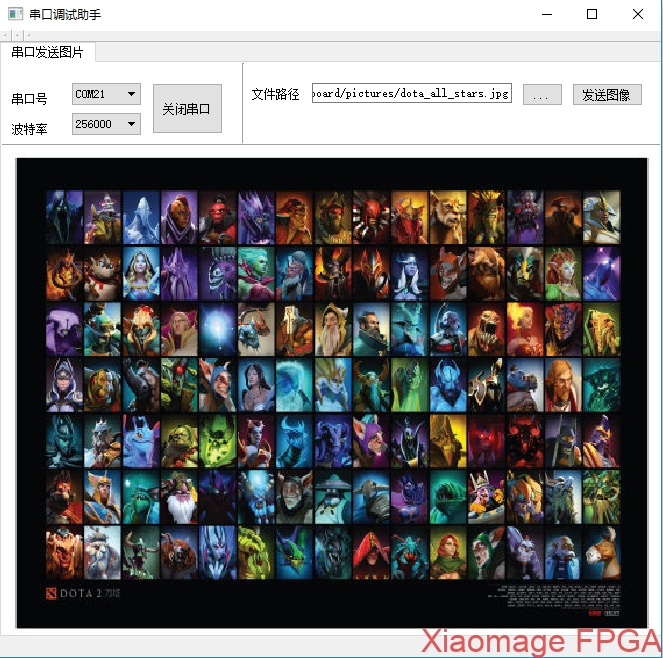

上位机效果

文章评论