功能介绍

- 用两块FPGA开发板设计一个曼彻斯特码编码和解码系统;

- 第1块板负责在按键后将拨码开关拨出的8位二进制码用曼彻斯特码发出;

- 第2块板负责在收到曼彻斯特码号将其解析并在数码管上显示。

软硬件环境

- 软件平台:Quartusii18.1(下载、安装和破解教程)

- 语言 :verilog hdl

- 硬件环境:DE2-115开发板

- 外设:按键、SW、GPIO

效果演示

讲解视频(视频较大,加载需要点时间,请耐心等待)

使用说明

- 信号说明

- 操作说明

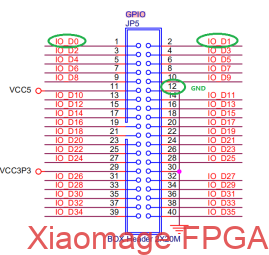

SW[7:0]代表需要发送的字节数据,接线时需要把发送端的GPIO_D0和接收端的GPIO_D1连接上,使用杜邦线连接,同时需要把两个开发板的GND连接到一起。拨动SW[7:0],观察接收端的FPGA开发板上的数码管数据变化。

版权声明

该代码为本站自研,拥有全部知识产权。

文章评论