项目介绍

- 硬件平台:无

- 软件平台:Quartusii18.1(下载、安装和破解教程)

- 语言 :verilog hdl

功能定义

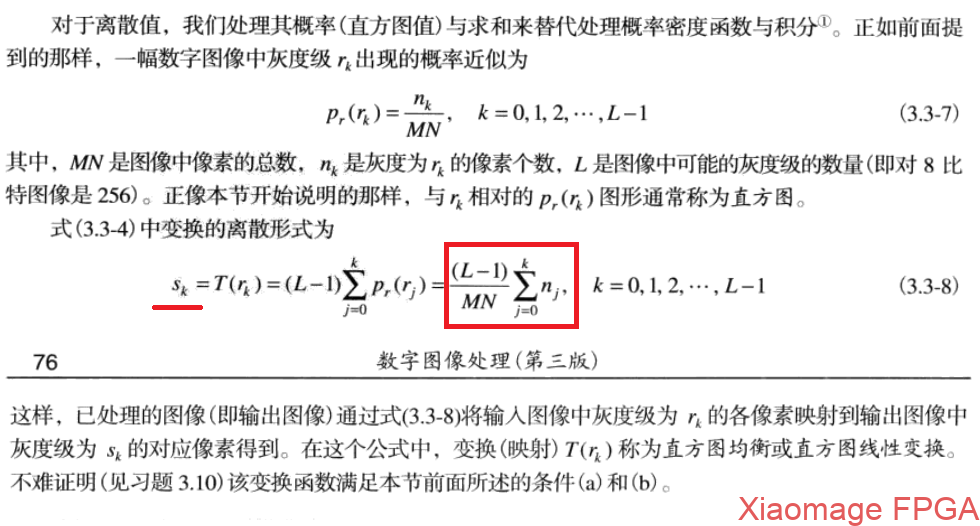

实现直方图均衡化算法

详细要求

- 分辨率最大支持640*480,且分辨率可设置;

- 输入和输出位宽为8bits(灰度图);

- Avalon-ST裸流视频接口;

使用说明

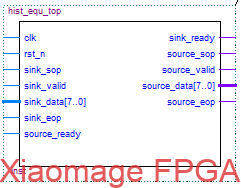

| 信号 | 方向 | 描述 |

| clk | input | 同步时钟 |

| rst_n | input | 异步复位,低有效 |

| sink_sop | input | 标志输入视频流一帧开始,高有效,需要sink_valid同时为高 |

| sink_valid | input | 输入数据有效标志信号,高有效 |

| sink_data[7:0] | input | 输入数据 |

| sink_eop | input | 标志一帧结束,高有效,需要sink_valid同时为高 |

| sink_ready | output | 可接收数据标志,高有效 |

| source_sop | output | 标志输出视频流一帧开始,高有效,需要source_valid同时为高 |

| source_valid | output | 输出数据有效标志信号,高有效 |

| source_data[7:0] | output | 输出数据 |

| source_eop | output | 标志输出视频流一帧结束,高有效,需要source_valid同时为高 |

| source_ready | input | 可以输出视频流的使能,由后级模块给予,高有效,为高时才可输出视频流数据否则停止输出 |

说明:

- sink_sop和sink_valid都为高对应一帧图像的第一个像素;

- sink_eop和sink_valid都为高对应一帧图像的最后一个像素;

- sink_ready为输出信号,高电平本模块可接收前级数据,否则本模块不可接收前级数据;

- source_ready为输入信号,需要外部后级模块提供,为高则表示本模块可以输出数据流,否则停止输出数据流;

调试记录

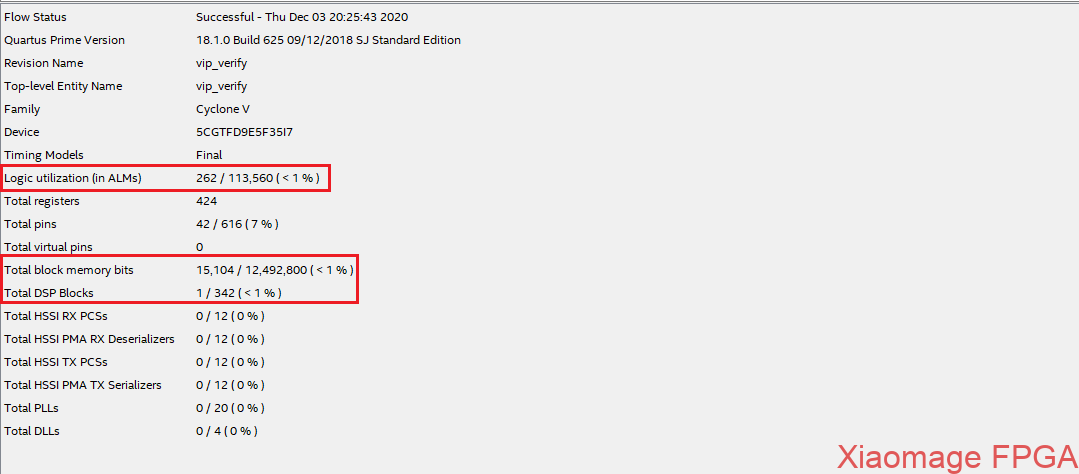

资源消耗:

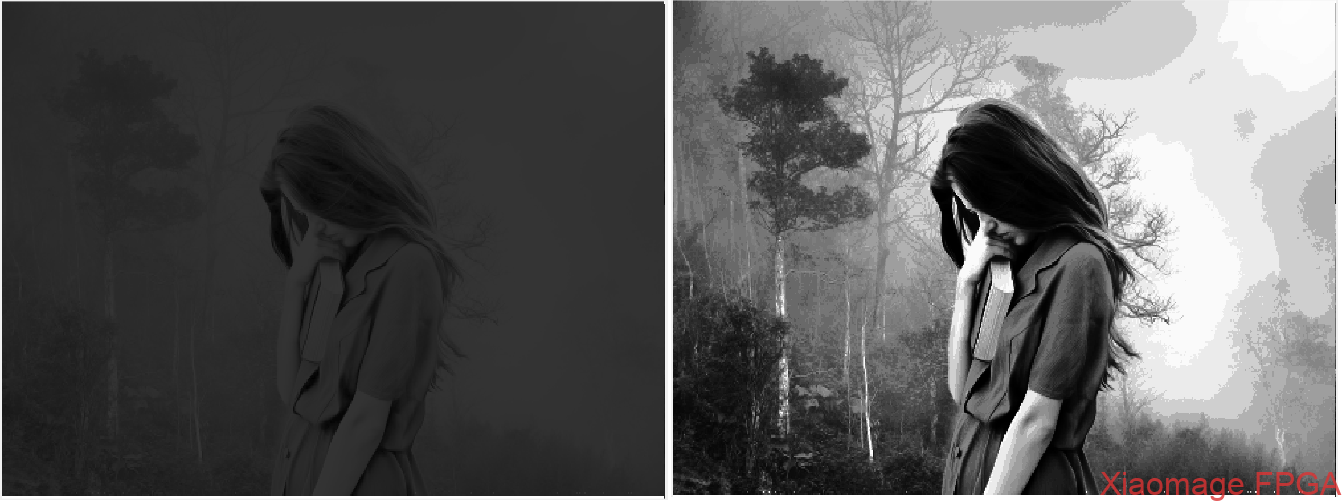

功能效果演示

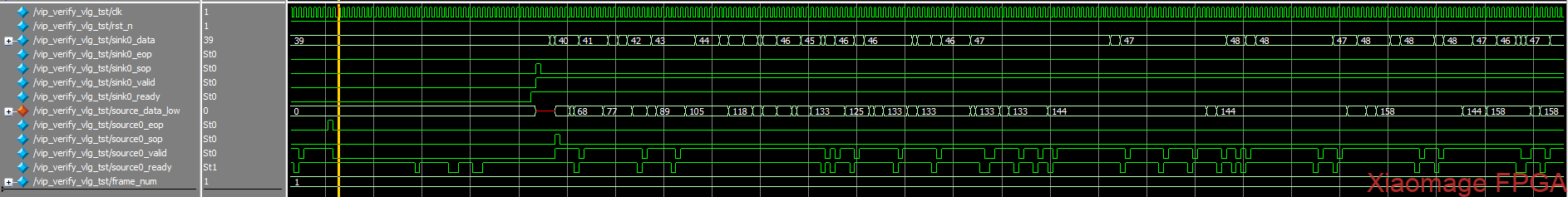

仿真效果

代码分享

百度网盘:https://pan.baidu.com/s/1M0i_wFC5Dw86lhVVSyVipQ

提取码:dmk0

文章评论