项目介绍

- 软件平台:Quartusii13.1

功能定义

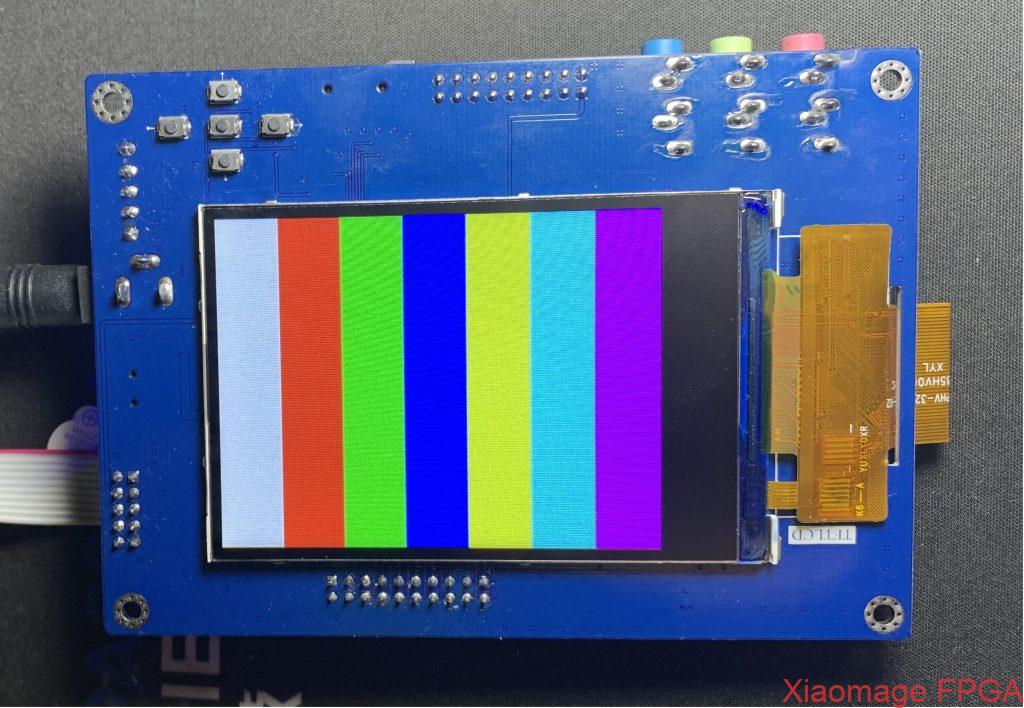

基于FPGA的ILI9488 TFTLCD显示屏驱动,Verilog语言源码,实现彩条显示。

详细要求

- 接口为16bits模式,8080接口;

- 分辨率480*320;

- 可任意坐标(x,y)画点;

- 实现彩条显示;

使用说明

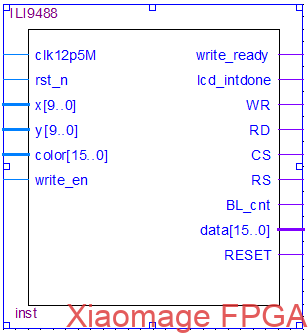

| 信号 | 方向 | 描述 |

| clk12p5M | input | 同步时钟,最大不超过12.5MHz |

| rst_n | input | 异步复位,低有效 |

| x[9:0] | input | 需要画的点的横坐标,范围0~479 |

| y[9:0] | input | 需要画的点的纵坐标,范围0~319 |

| color[15:0] | input | 需要画的点的颜色数据,RGB565格式 |

| write_en | input | 画点使能,高有效 |

| write_ready | output | write_en拉高后必须等待write_ready为高才表示颜色数据有效写入 |

| lcd_intdone | output | 标志TFTLCD初始化完成,高有效 |

| WR | output | 接TFTLCD屏的WR管脚 |

| RD | output | 接TFTLCD屏的RD管脚 |

| CS | output | 接TFTLCD屏的CS管脚 |

| RS | output | 接TFTLCD屏的RS管脚,该管脚为指令/数据选择管脚 |

| BL_cnt | output | 接TFTLCD屏的BL_cnt管脚 |

| data[15:0] | output | 接TFTLCD屏的data管脚 |

| RESET | output | 接TFTLCD屏的RESET管脚 |

使用说明:

给上需要画点的坐标x、y,需要画点的颜色color(RGB565),拉高write_en,若write_en为高且write_ready为高则代表画点成功,否则需要一直等待直到write_ready拉高为止才可接着画下一个坐标点

系统框图

暂无

软件模块框图

暂无

各子模块设计

暂无

调试记录

暂无

功能效果演示

实物效果

演示视频

暂无

代码分享

源码付费下载付款成功后自动显示网盘分享链接

源码付费下载

付款成功后自动显示网盘分享链接

文章评论