简介

本教程采用官方的usbps库sdk案例,实现zynq模拟U盘,U盘的存储空间由DDR3提供,因此该模拟U盘是掉电数据丢失的。

软件版本

Vivado2020.2+Vitis2020.2。

Vivado工程创建

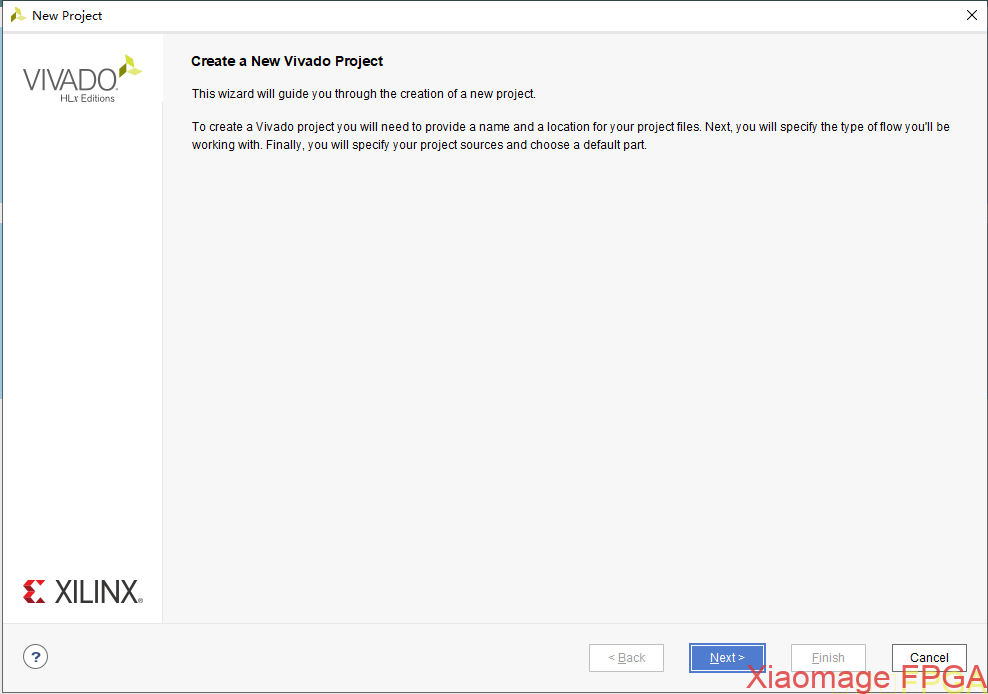

1.双击打开Vivado软件,点击“Create Project”--点击“Next”;

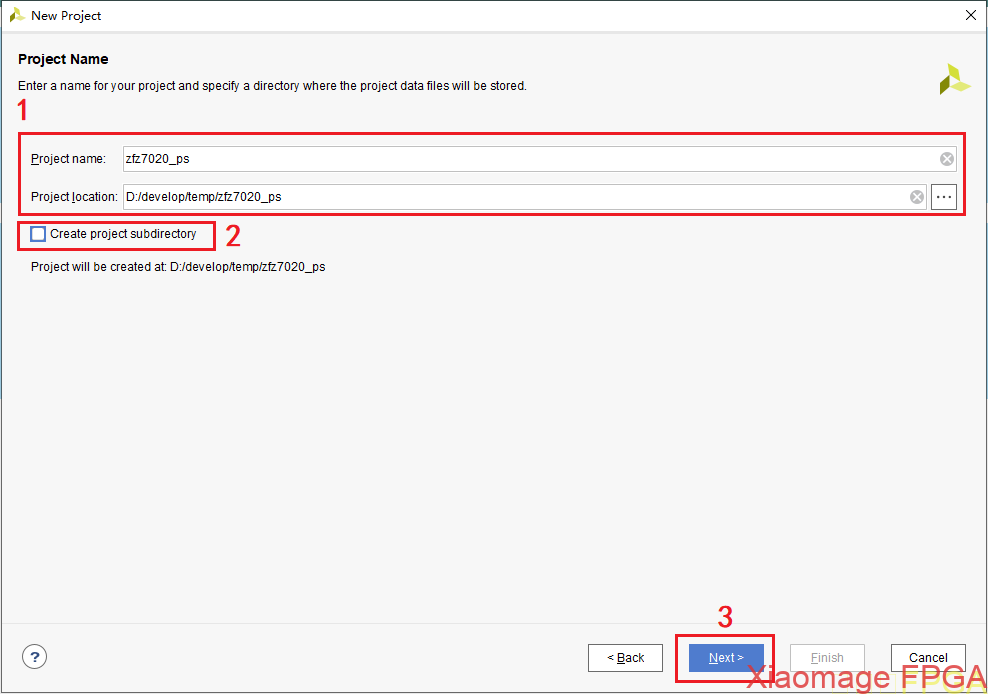

2.设置工程名和路径

a.在“Project name:”栏填入自定义的Vivado工程名称,注意不能含非英文字符;

b.在“Project location:”栏填入(或浏览到)工程想要存放的路径,同样的路径不能含非英文字符;

c.取消勾选"Create project subdirectory",否则软件会在路径下自动多生成一个同名文件夹;

d.点击“Next”;

3.点击“Next”;

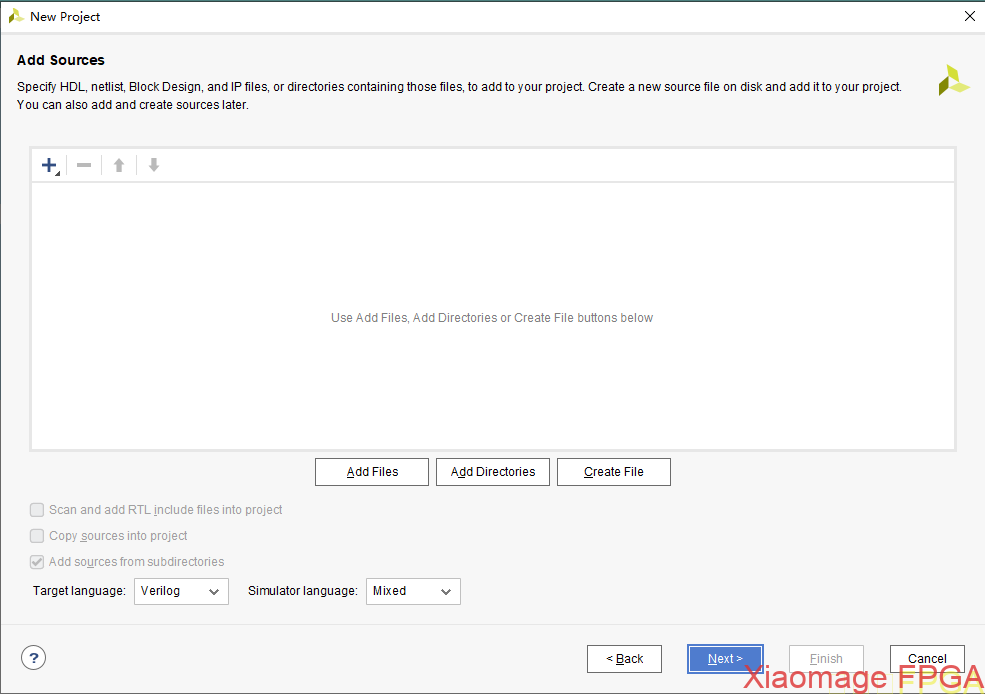

4.点击“Next”;

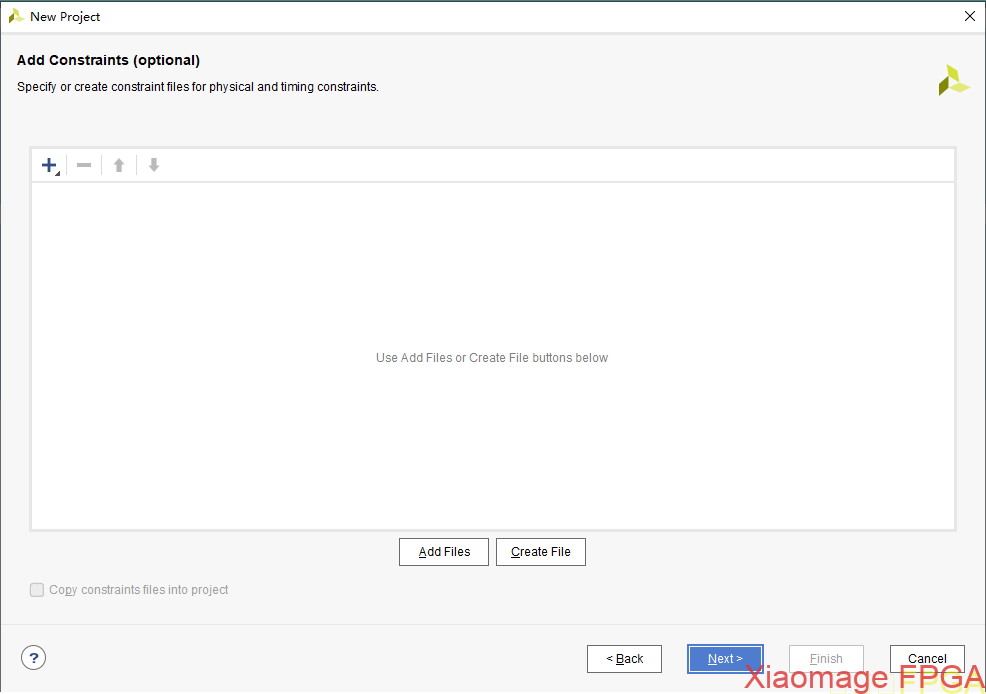

5.点击“Next”;

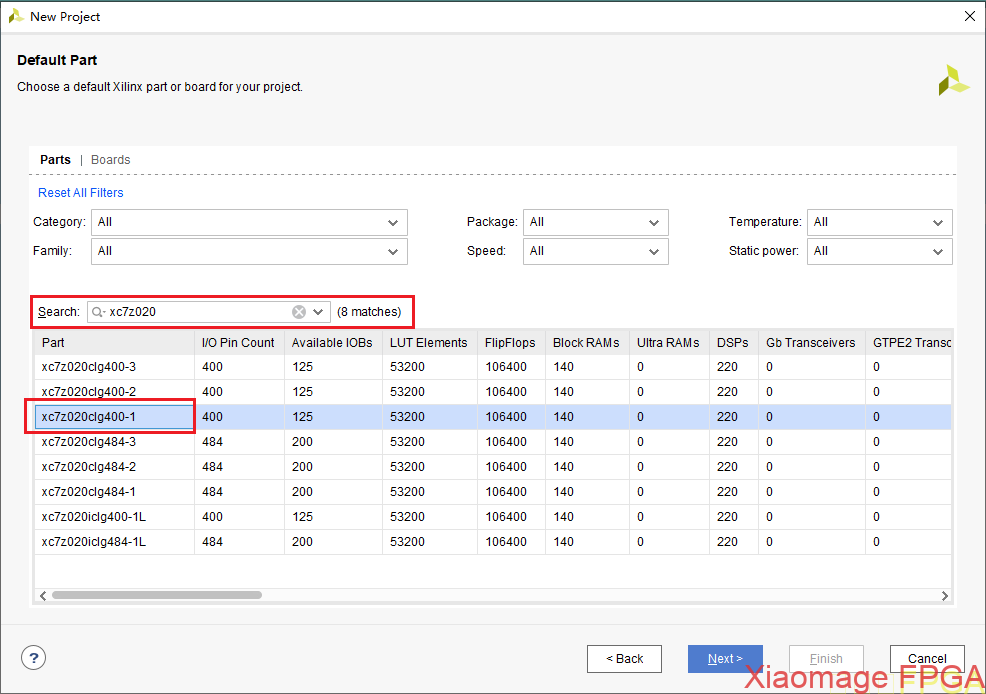

6.选择zynq器件型号,在搜索栏搜索:“xc7z020”--选择“xc7z020clg400-1”;

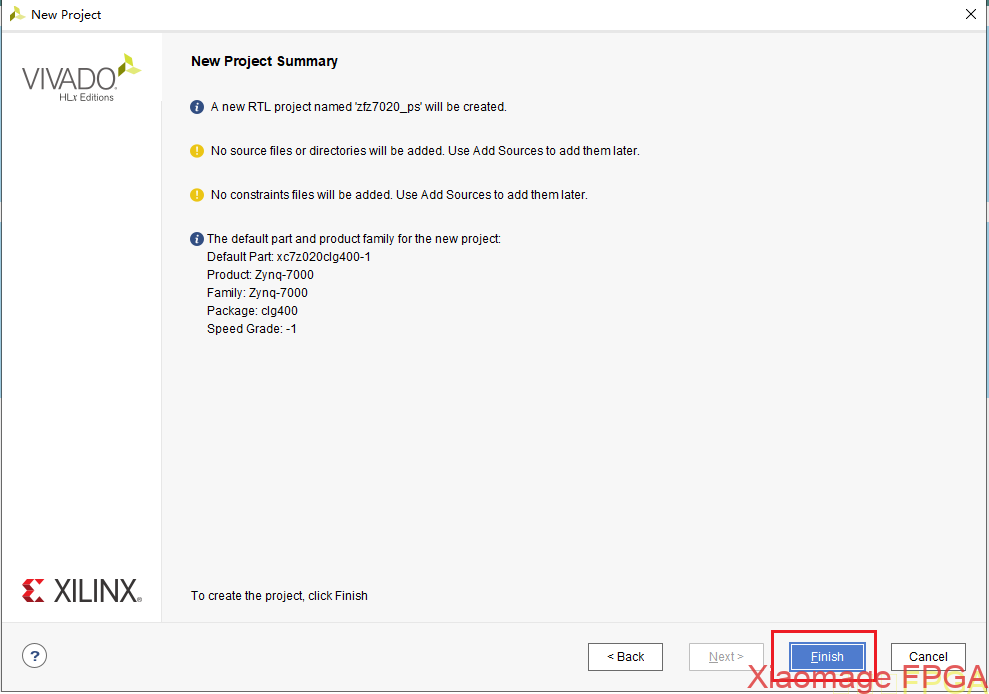

7.点击“Finish”;

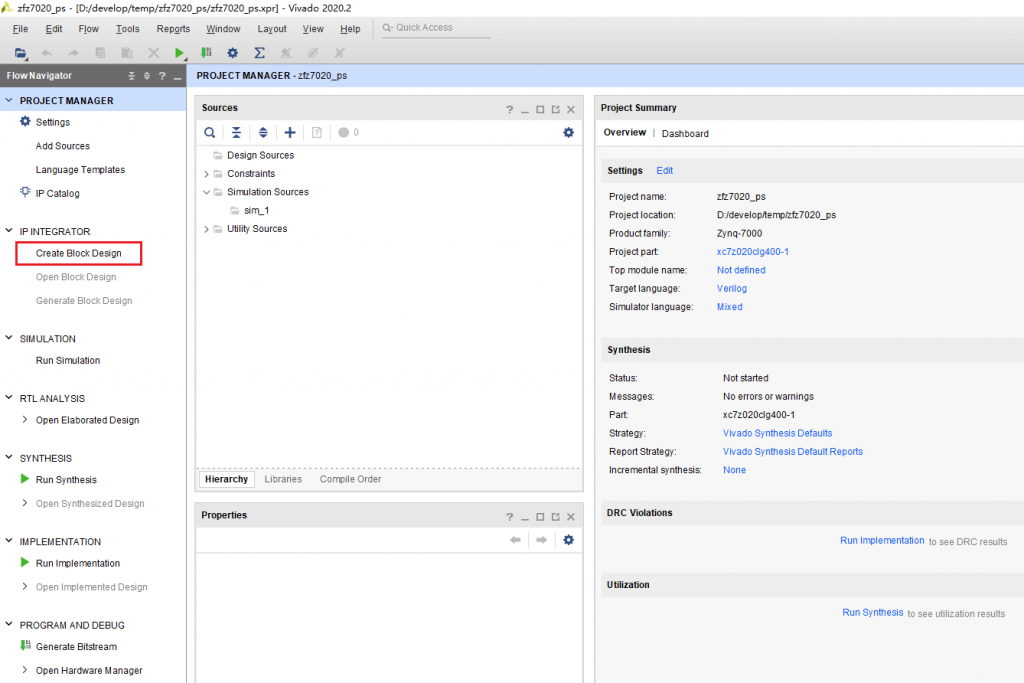

8.新建BD文件,点击“Creat Block Design”;

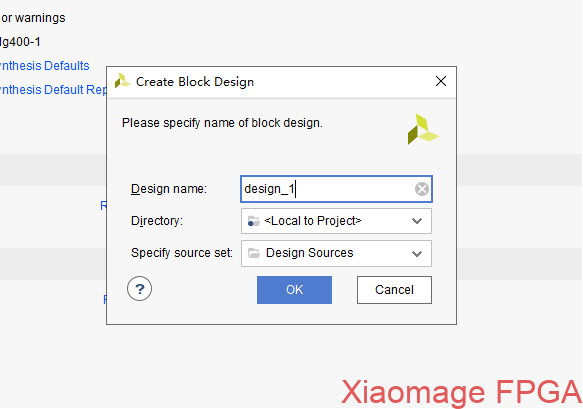

9."Design name"栏填入自定义的BD文件名,这里直接用默认名称,点击“OK”;

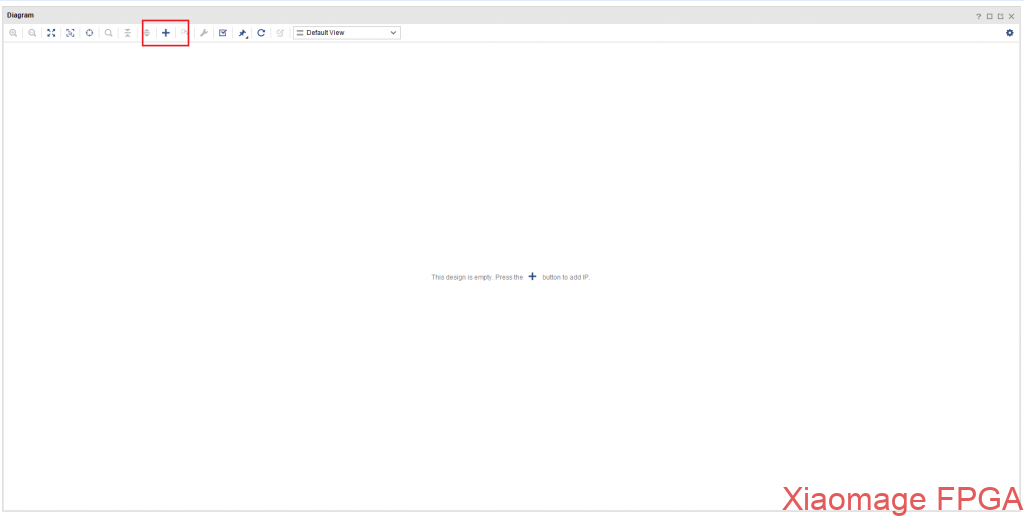

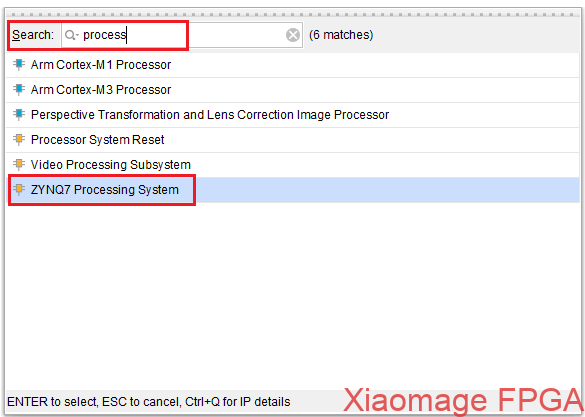

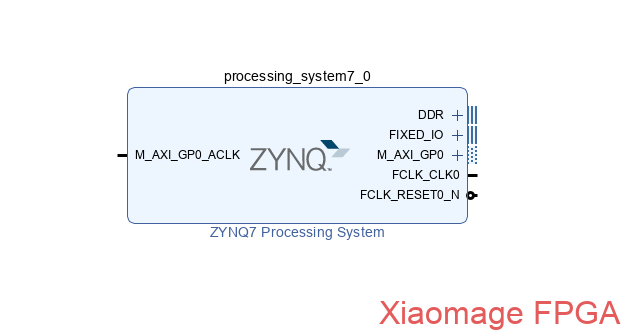

10.点击“+”添加zynq处理器系统的IP,搜索栏搜索“process”--双击“ZYNQ7 Processing System”;

11.此时BD文件中就添加好了zynq处理器系统的IP,接下来还需要对该IP进行设置;

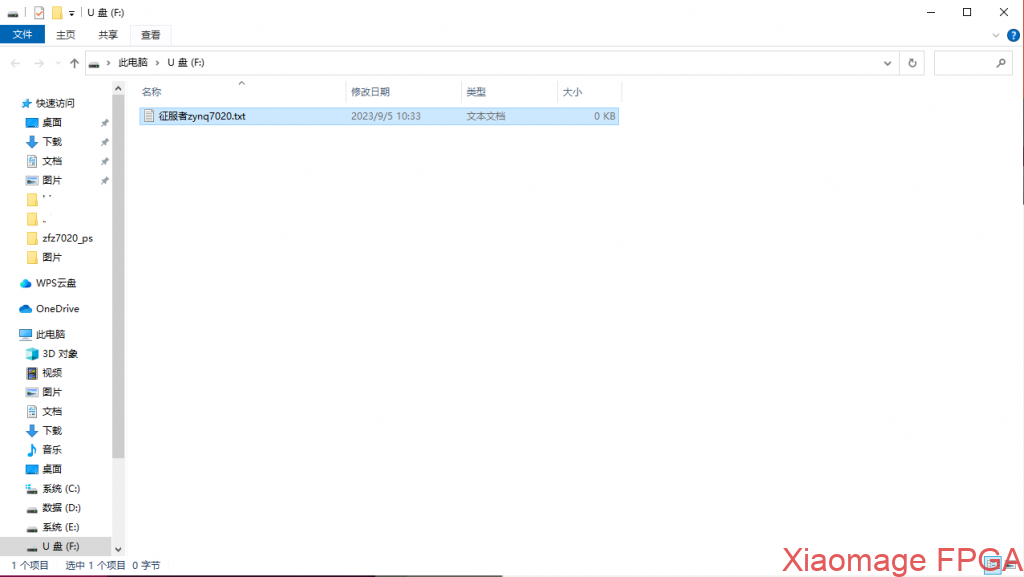

12.双击zynq处理器IP模块,进入设置界面;

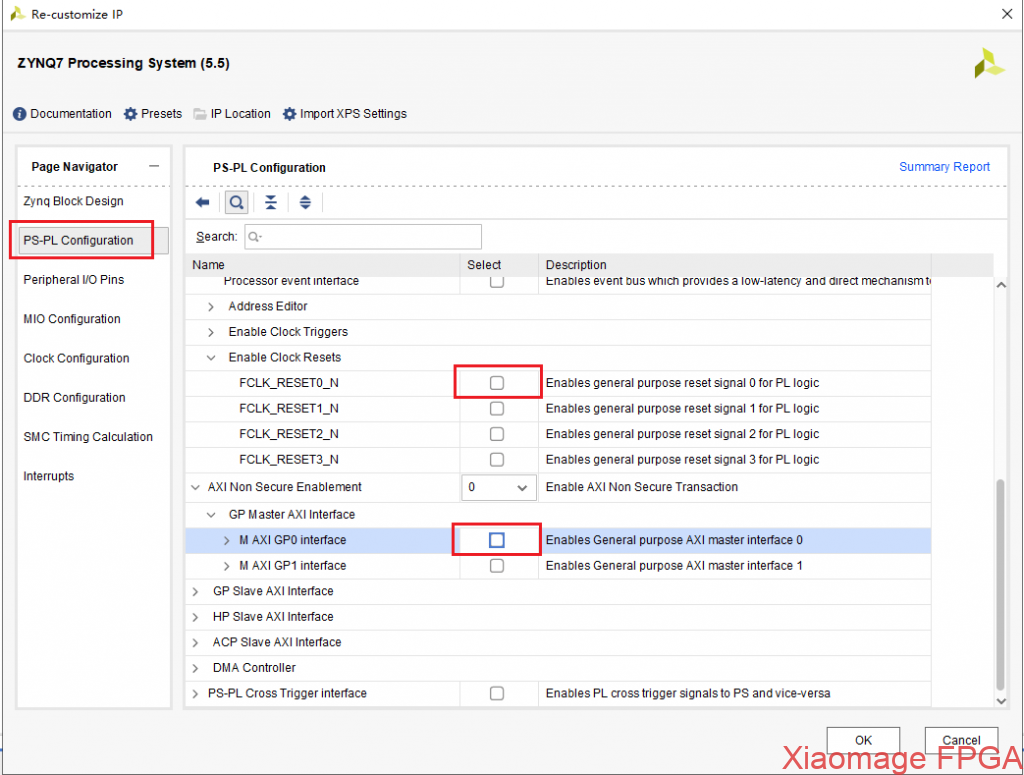

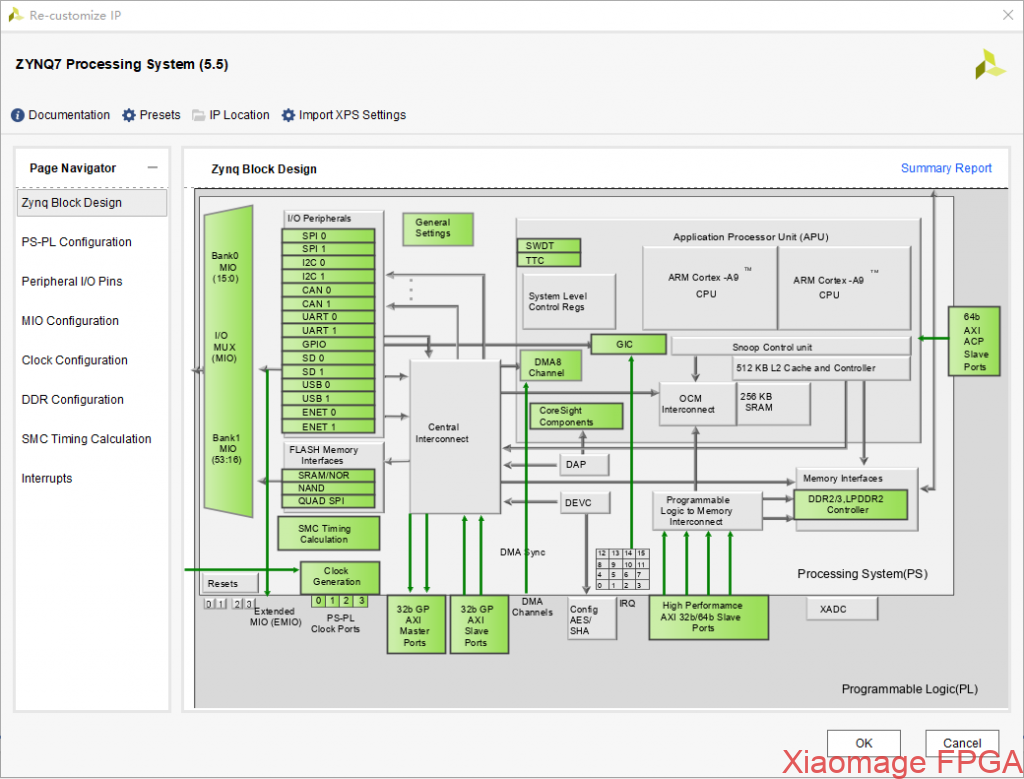

13.本设计只使用纯PS侧,因此取消勾选PS侧和PL侧之间的相关接口,使系统更简洁 ;

;

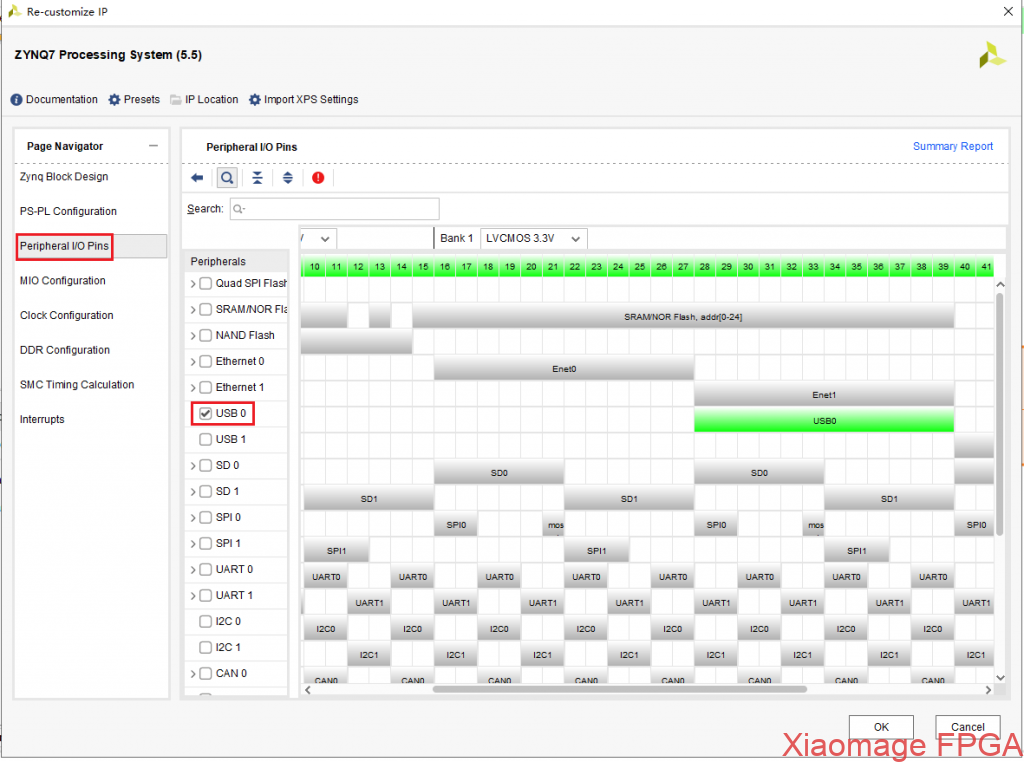

14.添加USB0外设;

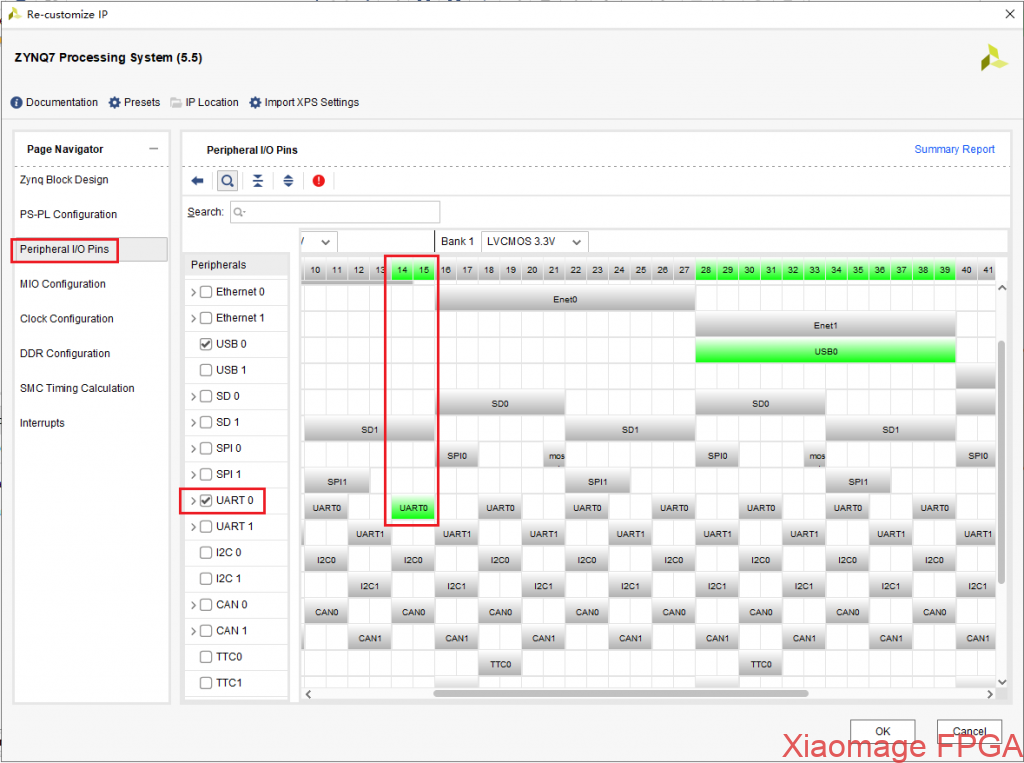

15.添加UART0外设,征服者zynq7020开发板硬件上UART0接的是MIO14和MIO15,所以这里选择MIO14和MIO15;

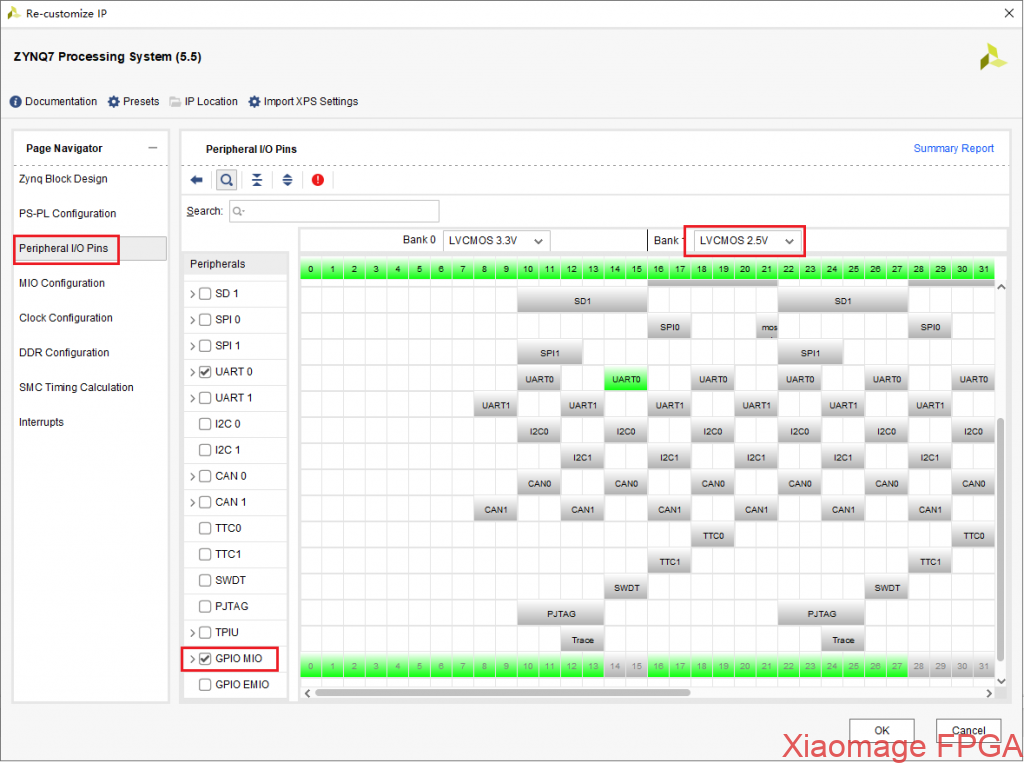

16..添加GPIO MIO外设,此处注意将BANK 1的电压标准改为LVCMOS 2.5V,原因是PS侧的以太网接口(在BANK 1)必须用2.5V或1.8V标准才能达到千兆网速,征服者zynq7020开发板硬件上使用的是2.5V标准,此处必须修改否则后面下载程序会报错;

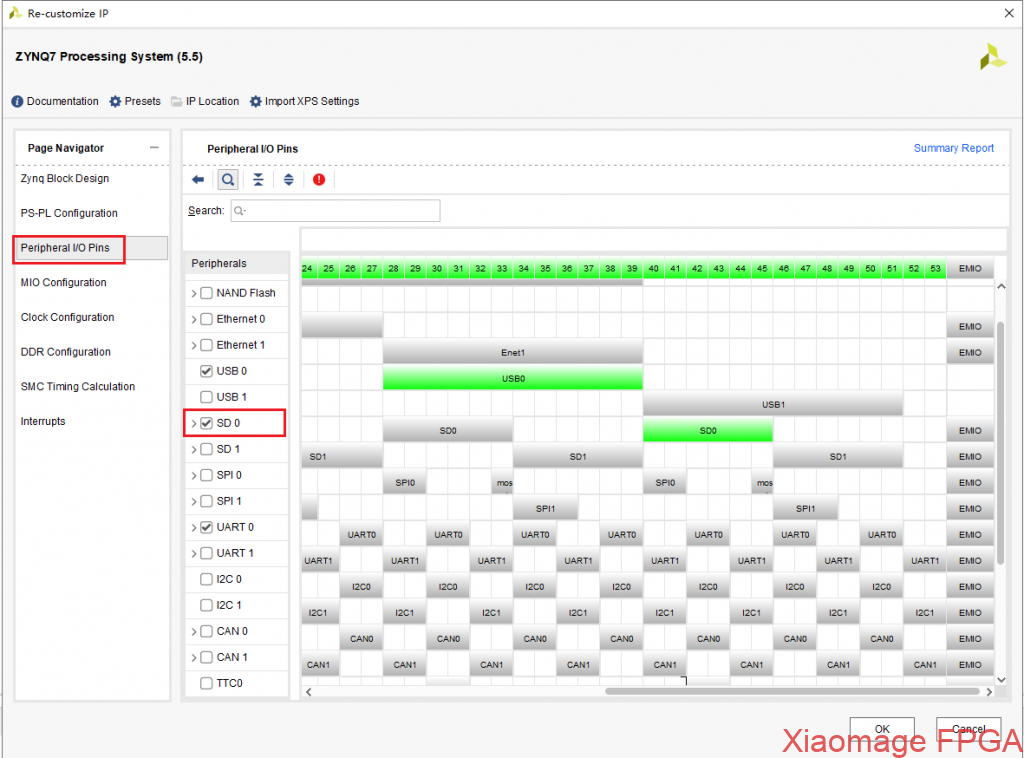

17.我们再额外勾选下SD0,不勾选SD0也是可以用JTAG下载程序调试的,但是就没办法SD卡方式启动;

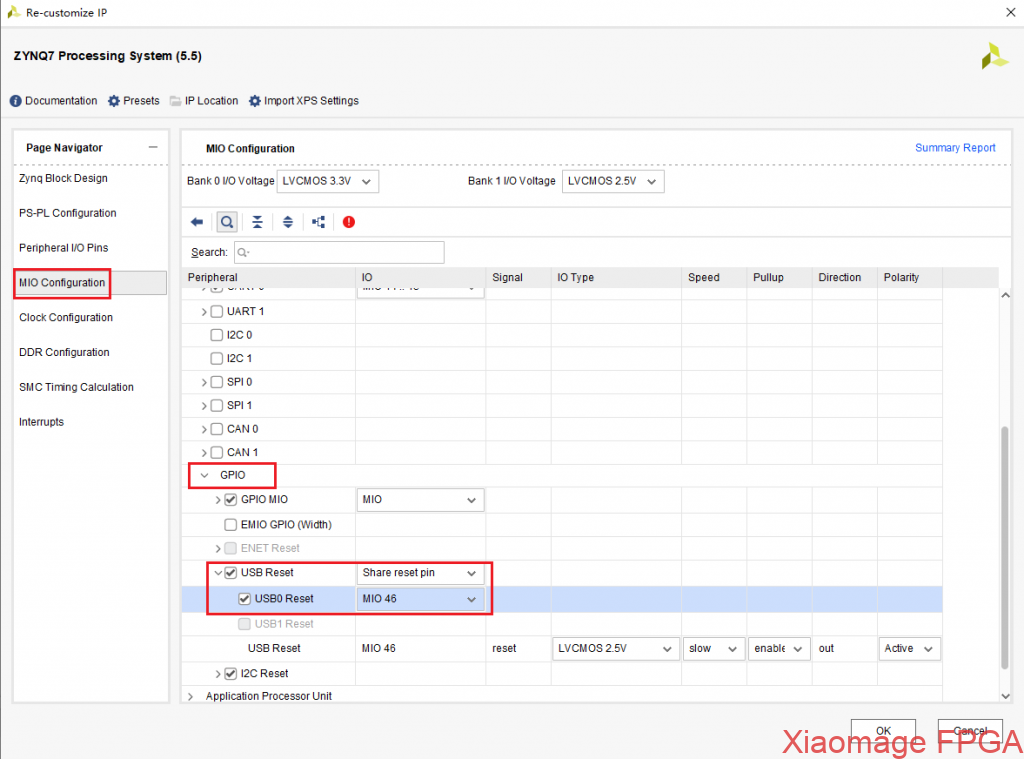

18.接下来设置下USB PHY芯片的复位管脚,在原理图中找到USB2232这颗PHY芯片,可以发现该芯片的复位管脚连接在zynq的MIO46管脚上,因此此处选择MIO46作为USB Reset;

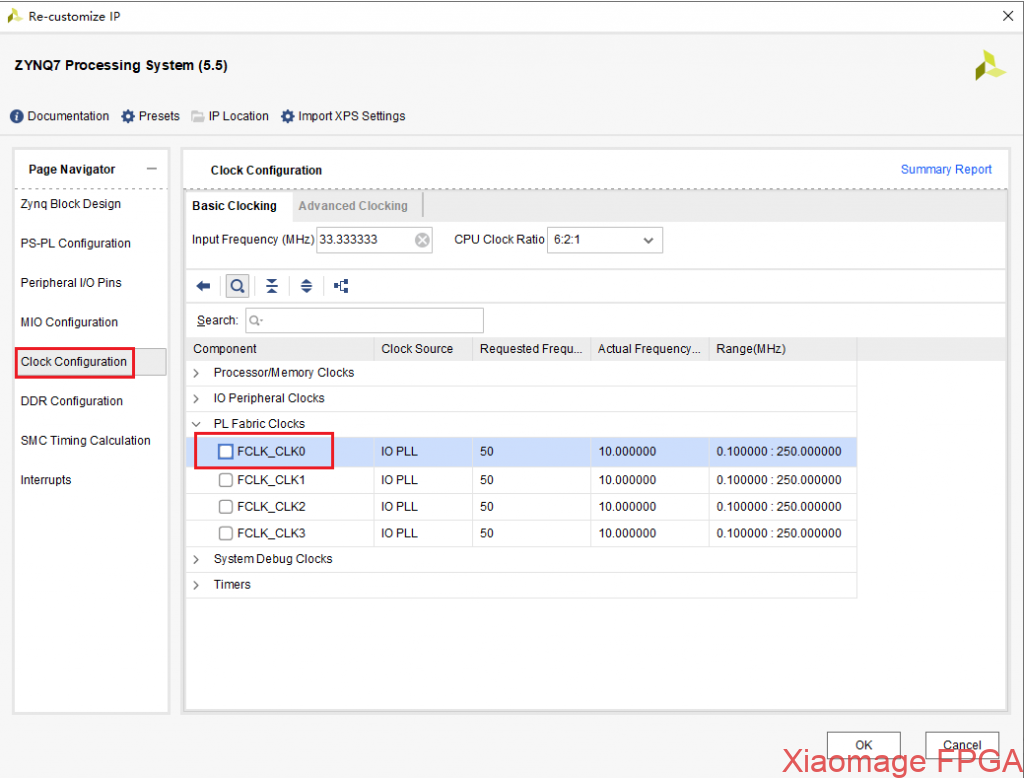

19.配置时钟,这里用不到PL侧,所以取消勾选"FCLK_CLK0";

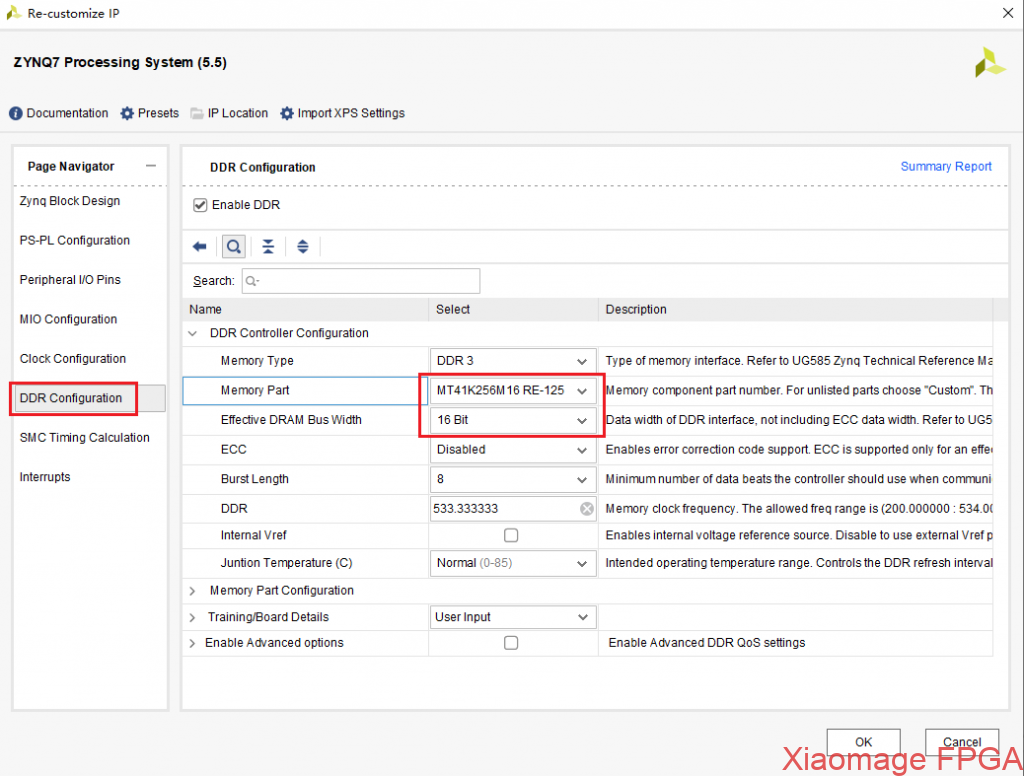

20.配置DDR3控制器参数,修改DDR型号和位宽16bits,修改完成后点击”OK“;

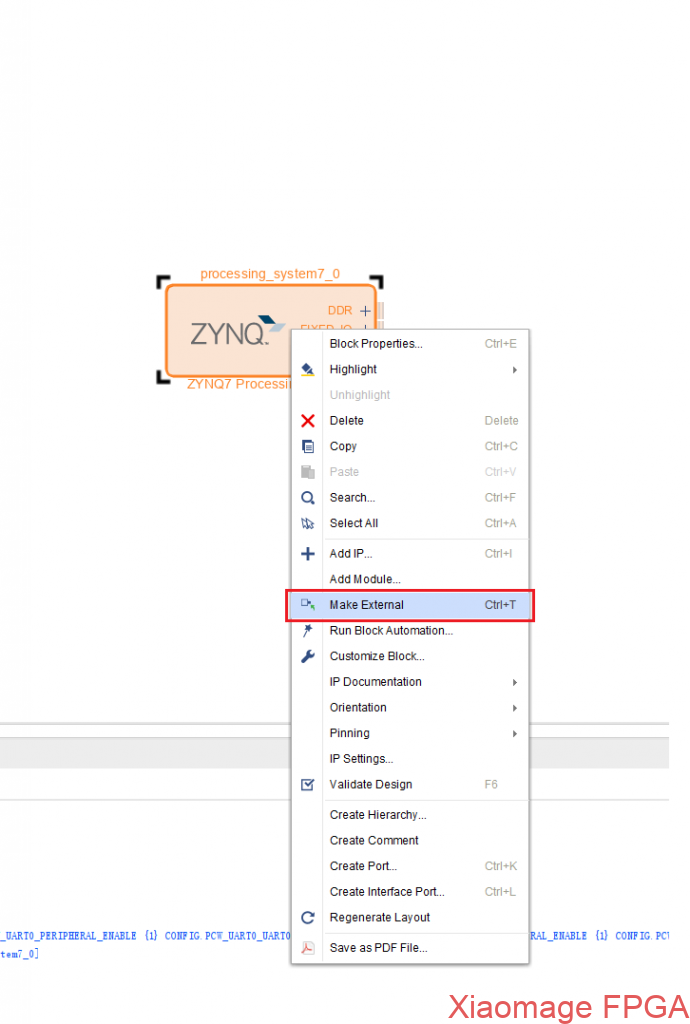

21.此时zynq处理器的IP配置就完成了,右键zynq处理器--点击"Make External"自动生成对外管脚连接信号;

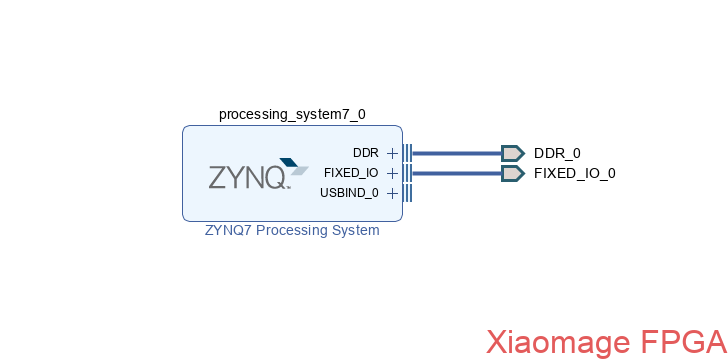

22.删除用不到的USBIND_0的管脚,得到最终如下图所示的模块;

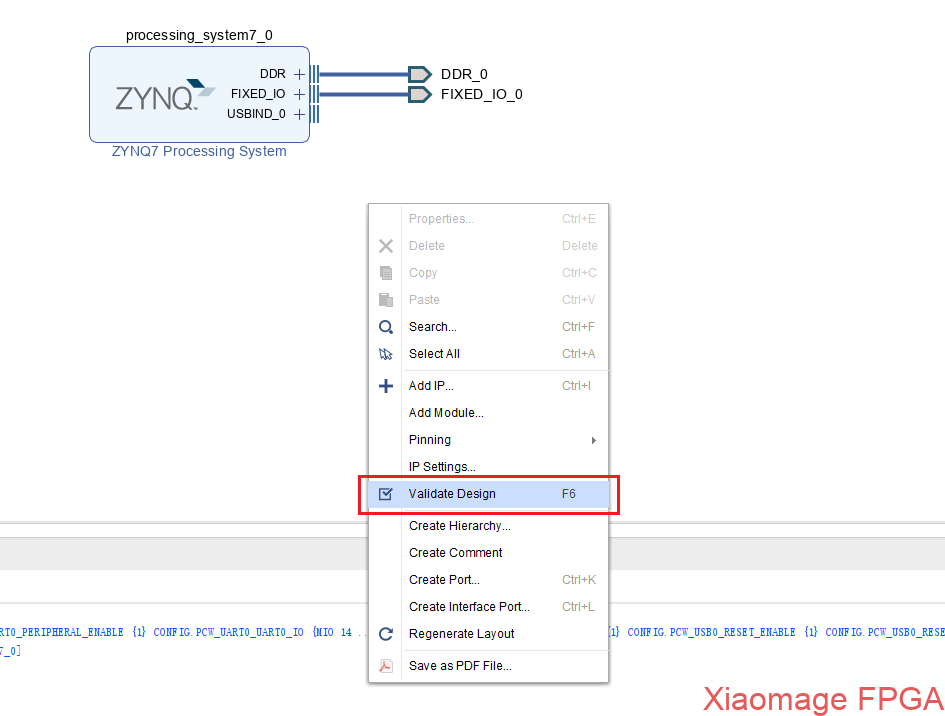

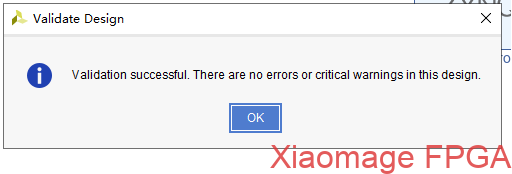

23.右键空白处--点击"Validate Design";

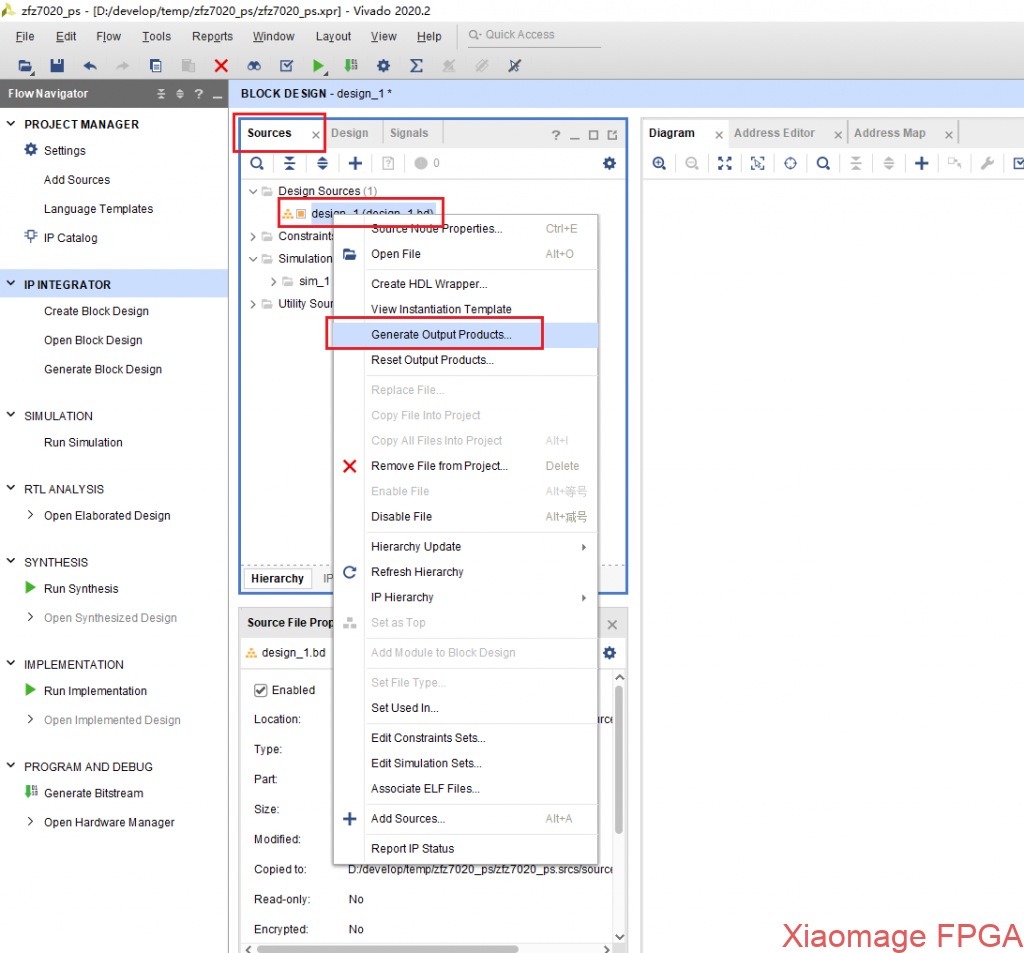

24.在source界面中右键BD文件--点击"Generate Output Products";

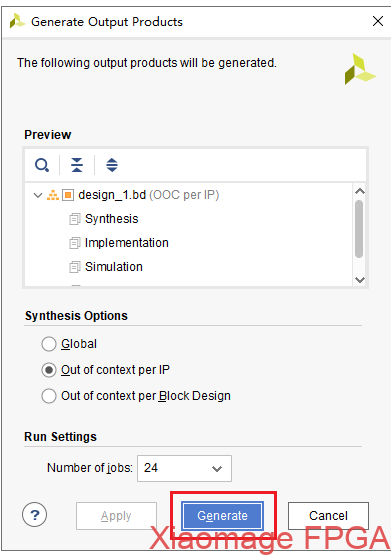

25.点击"Generate";

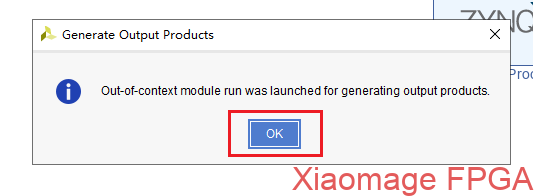

26.点击"OK";

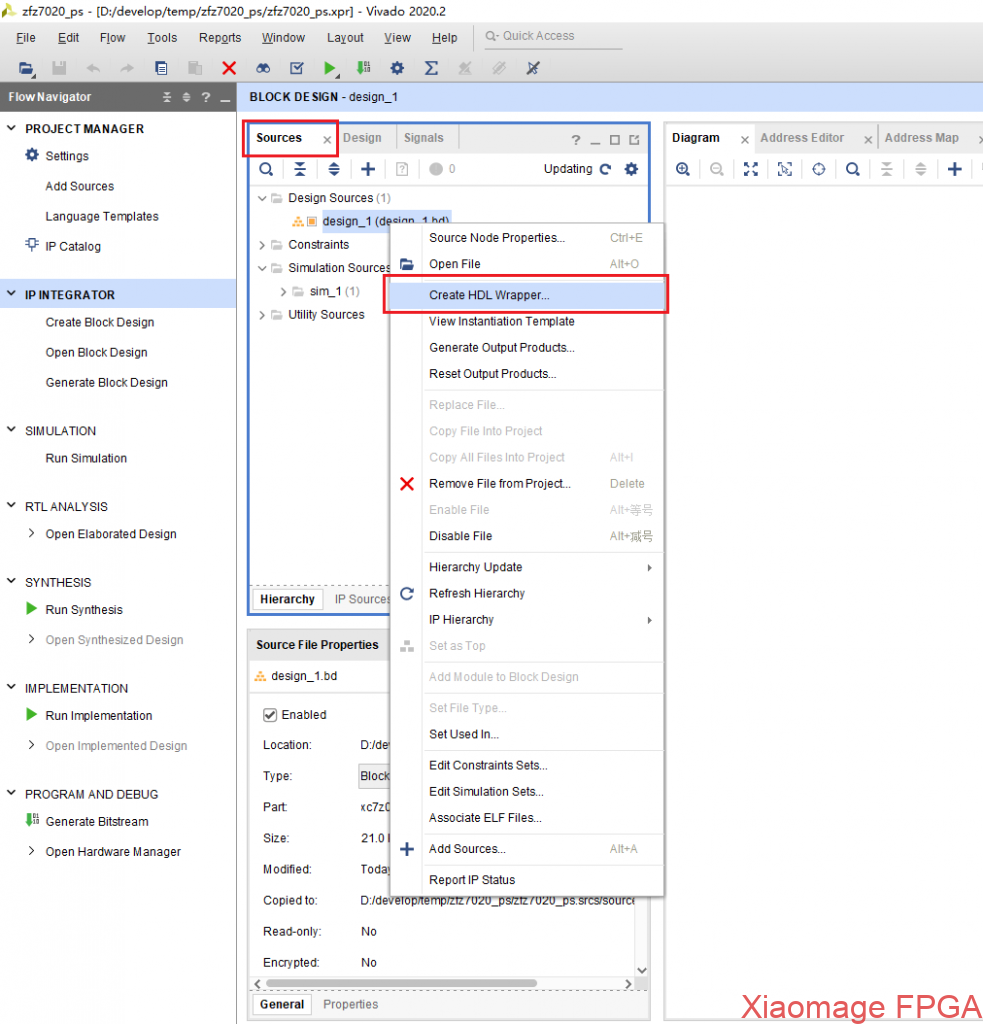

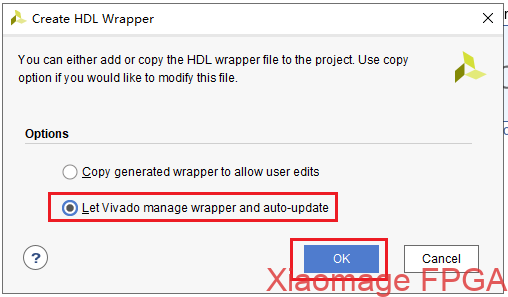

27.再次右键BD文件--点击"Create HDL Wraper...";

28.点击"OK";

29.至此,Vivado工程的建立就完成了,接下来进行Vitis SDK代码设计。

Vitis SDK程序设计

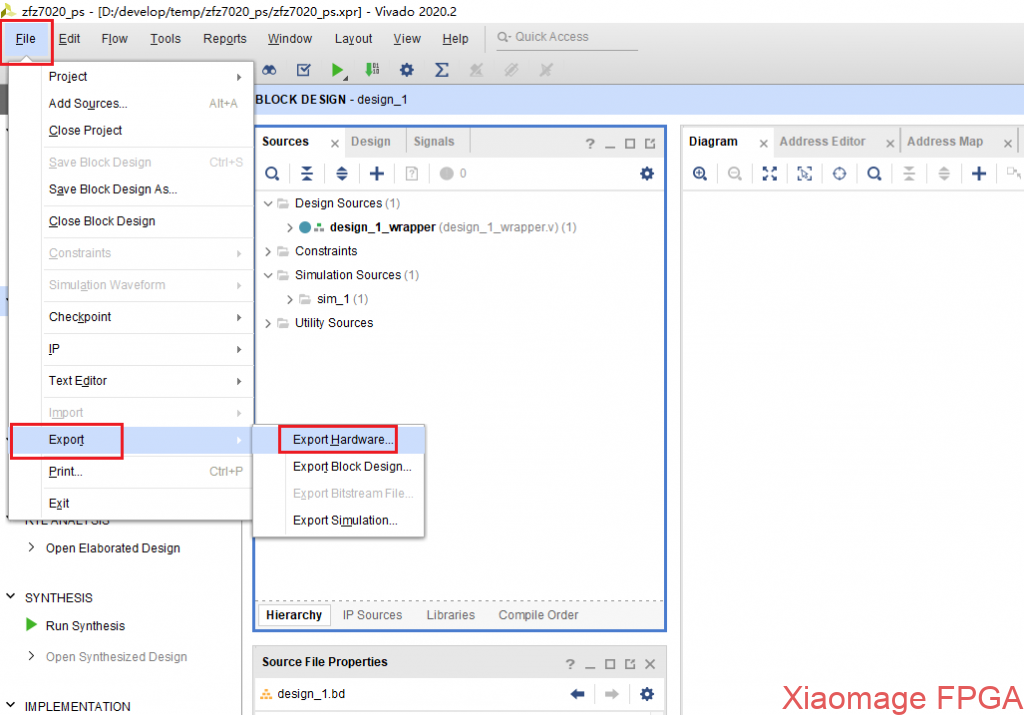

1.在Vivado工程中点击"File"--"Export"--"Export Hardware";

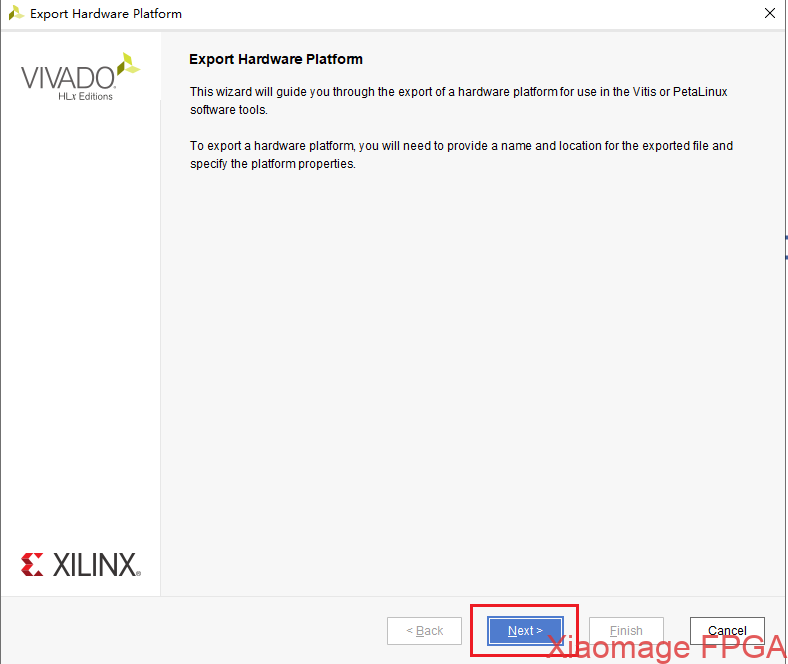

2.点击"Next";

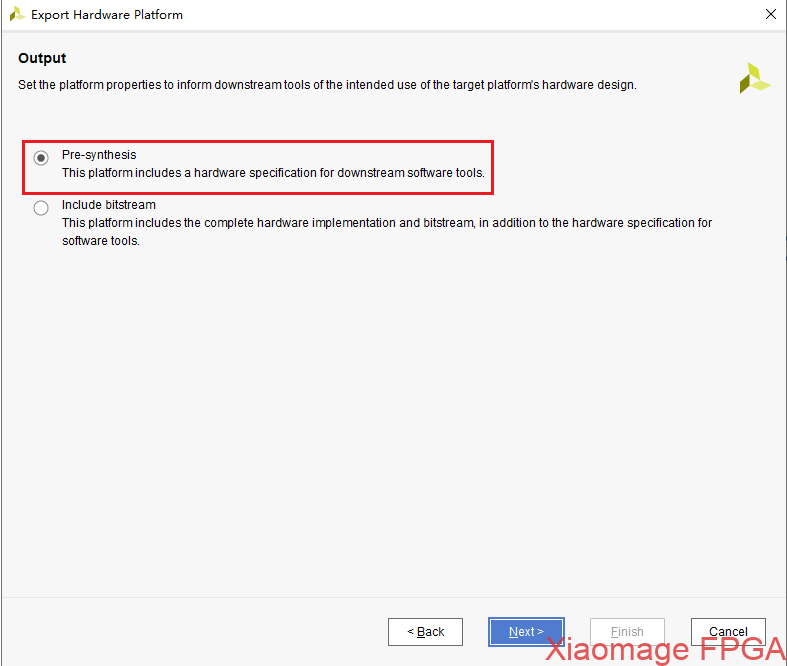

3.选择"Presynthesis"--点击"Next",因为是纯PS程序开发,不需要用到FPGA的bit文件;

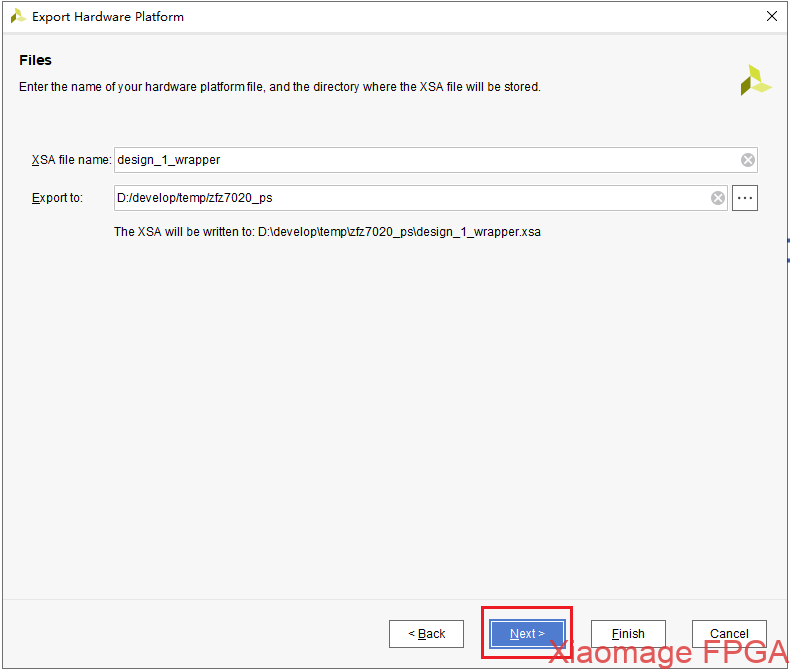

4.使用默认名称即可,点击"Next";

5.点击"Finish";

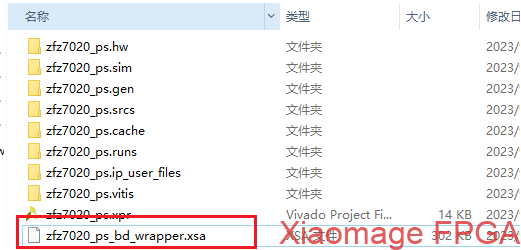

6.此时在Vivado的工程一级目录下新生成了一个后缀.xsa的文件,这个文件是Vitis需要用到的硬件描述文件,类似于老的Vivado版本的.hdf文件;

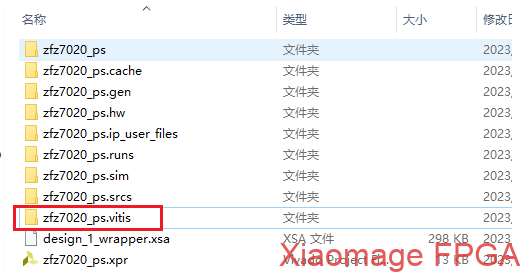

7.在Vivado的工程一级目录新建一个文件夹,命名为:zfz7020_ps.vitis,作为后续Vitis的workspace空间;

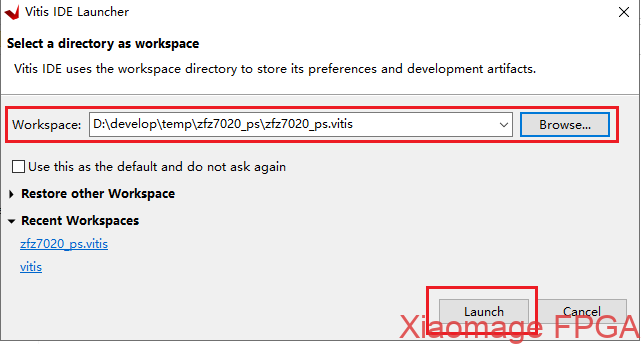

8.双击打开Vitis2020.2,点击"Browse.."--浏览到zfz7020_ps.vitis文件夹--点击"Launch";

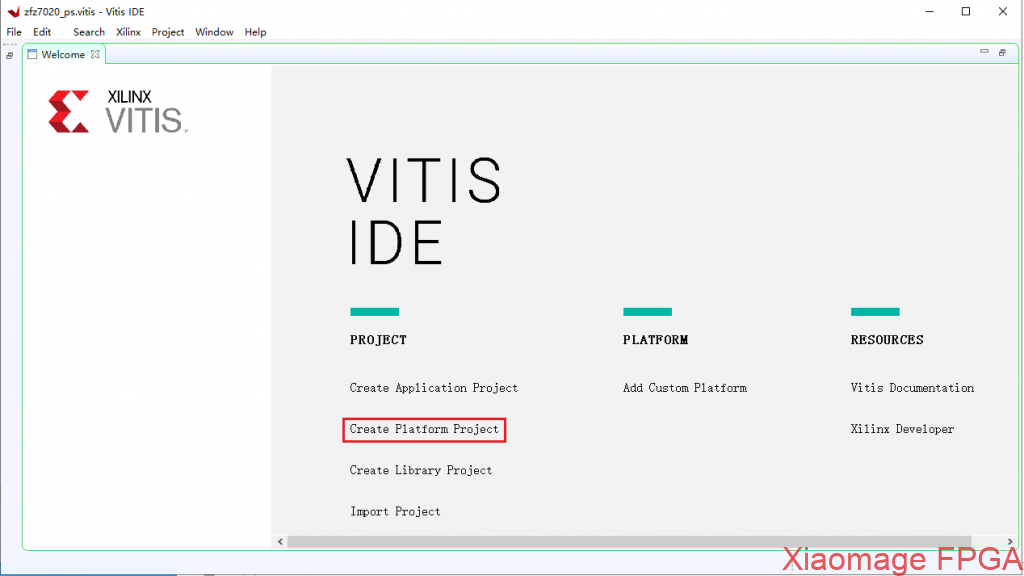

9.点击"Create Platform Project";

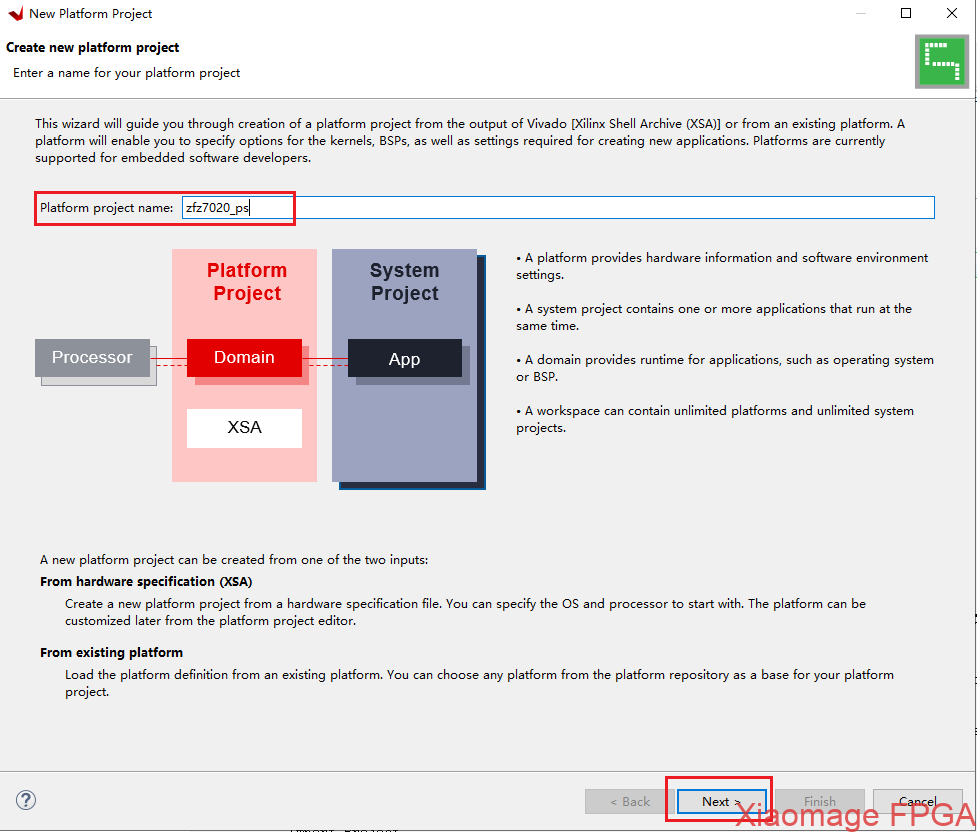

10.填入自定义的名称--点击"Next";

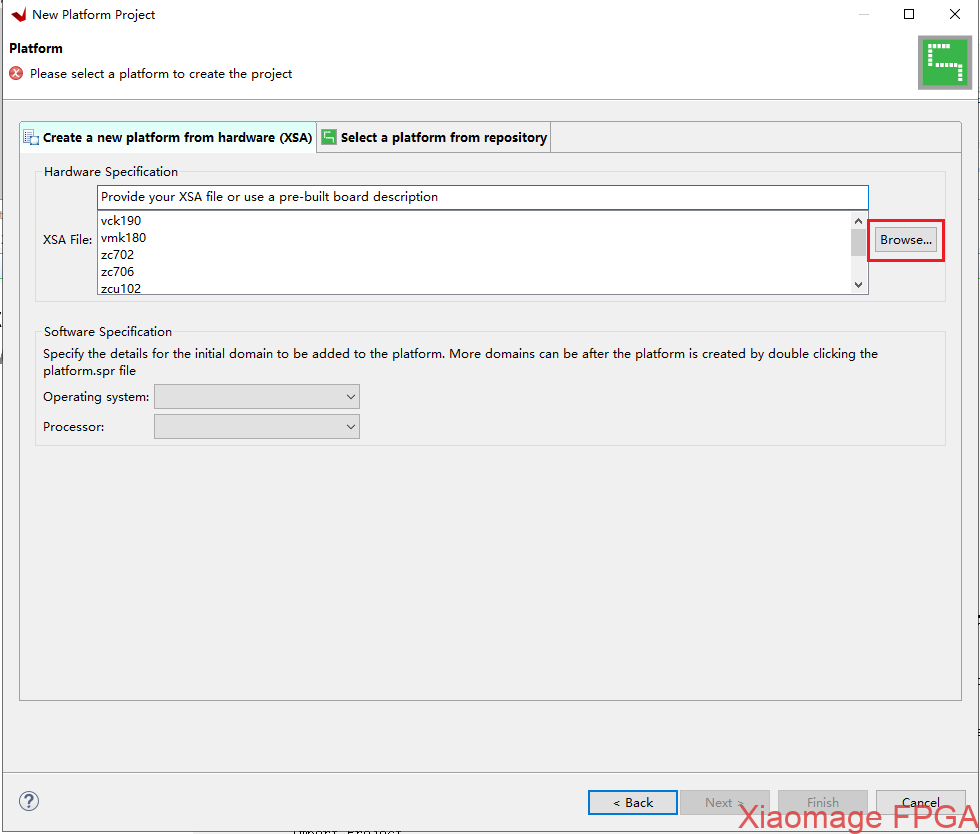

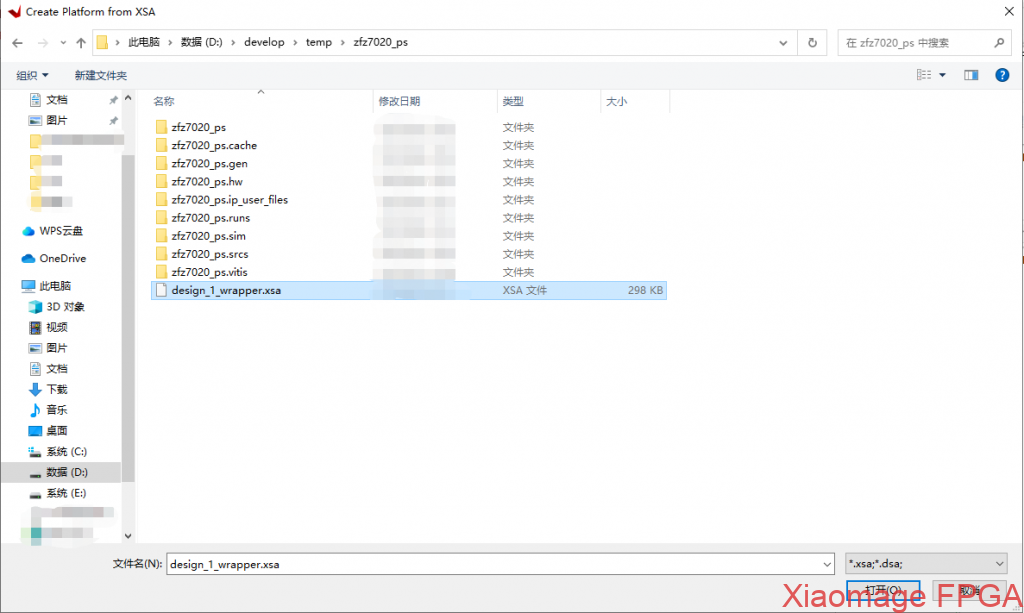

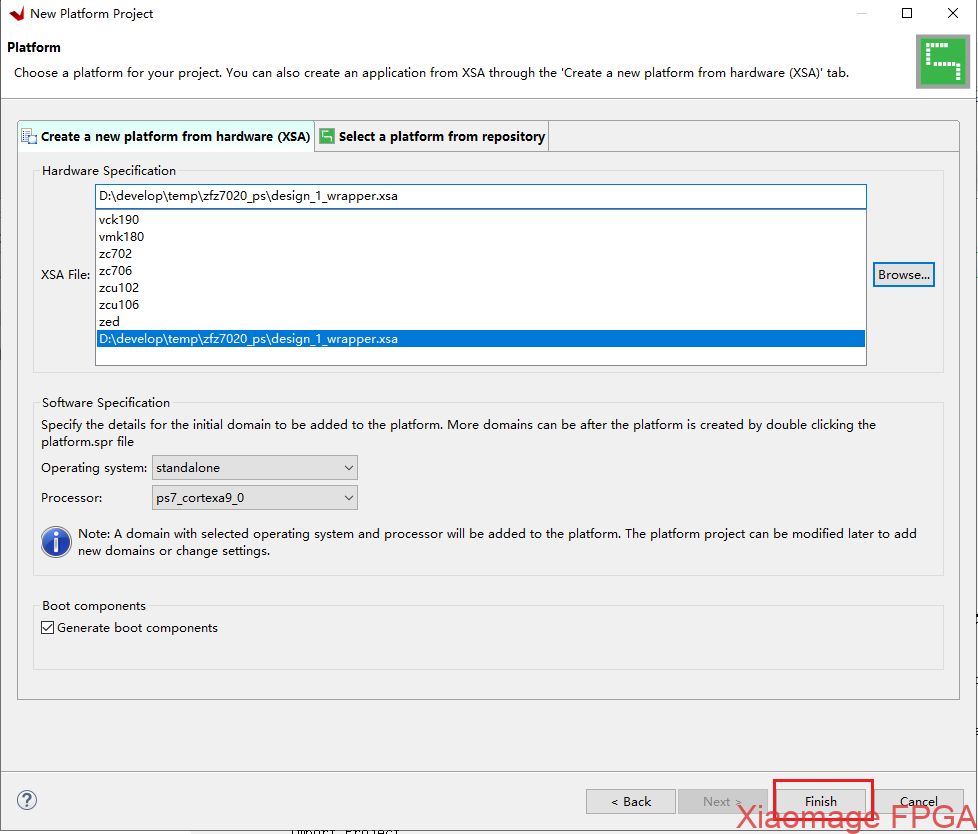

11.点击"Browse"浏览到步骤6中生成的.xsa文件;

12.点击"Finish";

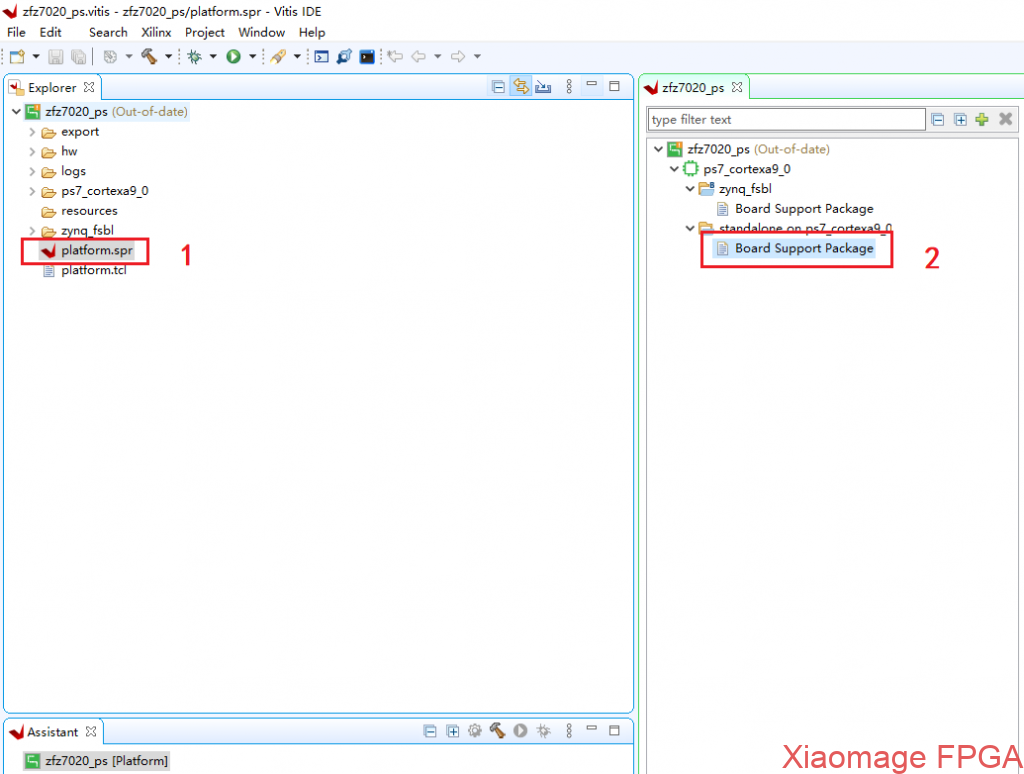

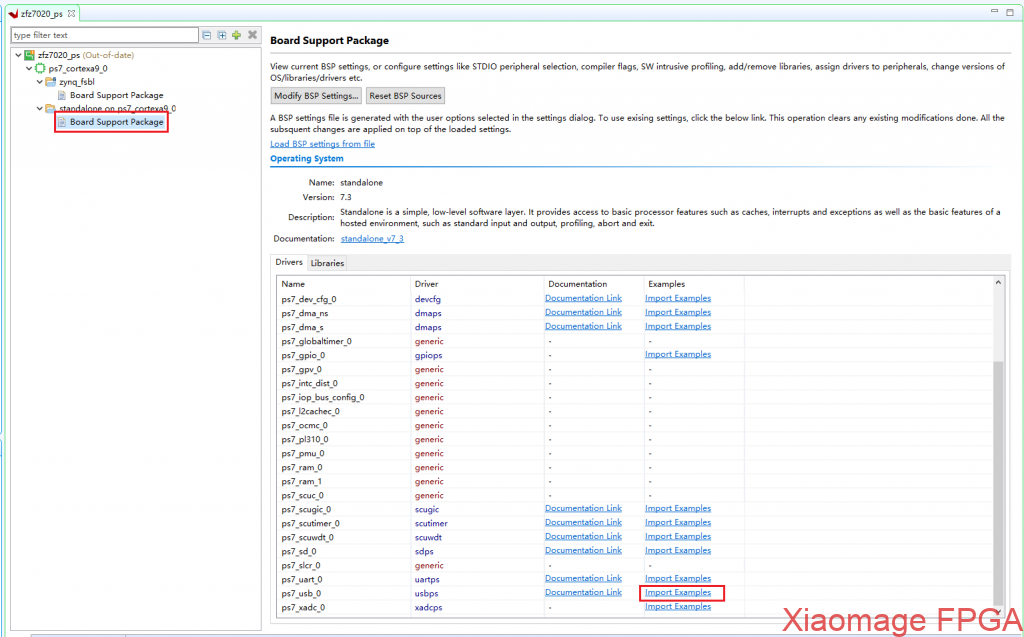

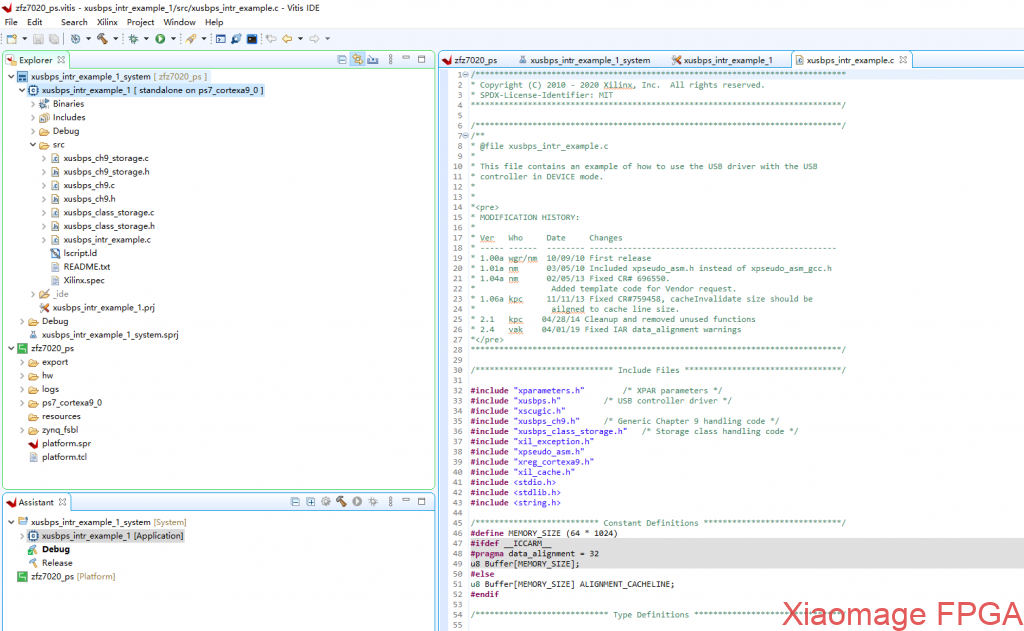

13.在Vitis界面中一次点击下图标注位置,导入官方usbps例程;

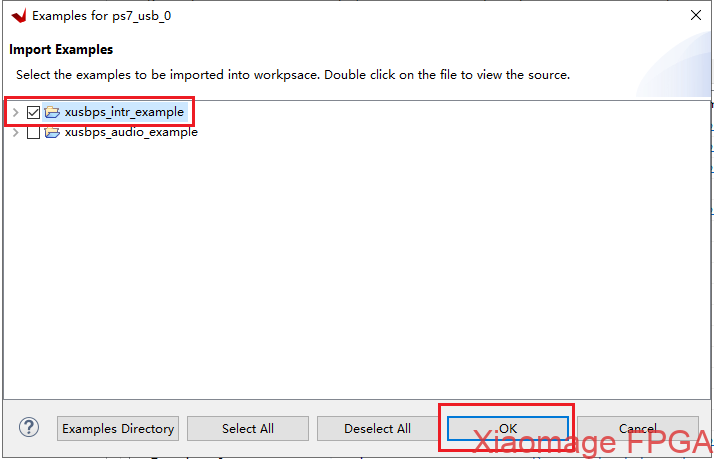

14.勾选上面这个--点击"Finish";

15."Ctrl+B"编译工程;

16.用两根Type-C线分别连接征服者zynq开发板的jtag和usb-device接口到电脑上;

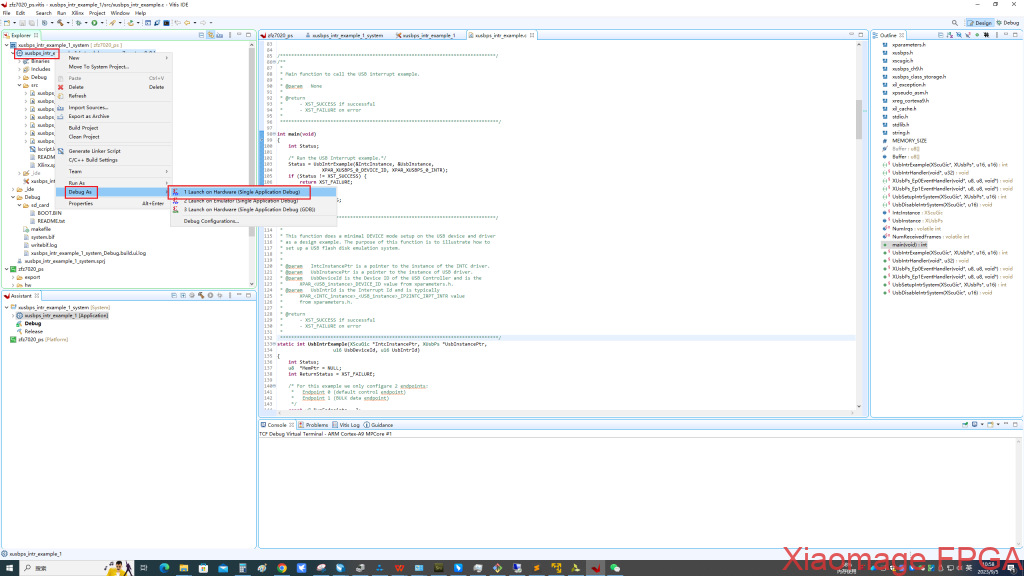

17.右键下图所示位置,将程序debug到开发板中;

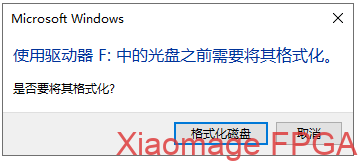

18.程序下载完毕,电脑上会自动弹出下图提示,检测到新的U盘,询问是否格式化,点击"格式化磁盘";

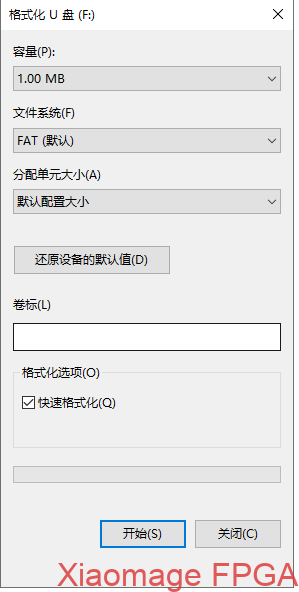

19.按照下图配置,将U盘格式化为FAT32格式;

20.接着在"我的电脑"中就可以查看到U盘,打开U盘并随便新建一个文件验证一下(注意zynq模拟的U盘是掉电易失的,不用存放任何有价值的文件);

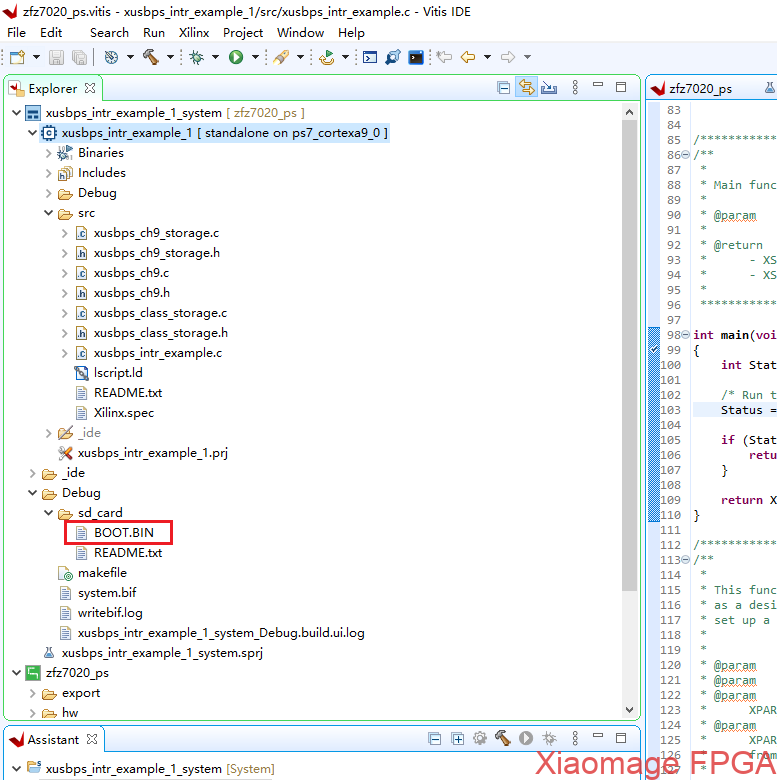

21.至此zynq模拟U盘的Vitis软件设计和实验就完成了,当然我们还可以在如下位置找到SD卡启动文件,Vitis默认的配置会自动产生SD卡启动的BOOT.bin,和老版本的SDK相比简化了生成SD启动文件的步骤;

22.将SD卡格式化为FAT32格式,并将BOOT.bin文件拷贝到SD卡中(需要用到读卡器),然后将SD卡插入到开发板的卡槽中重新给板子上电,就可以实验从SD卡启动zynq模拟U盘的功能了;

文章评论