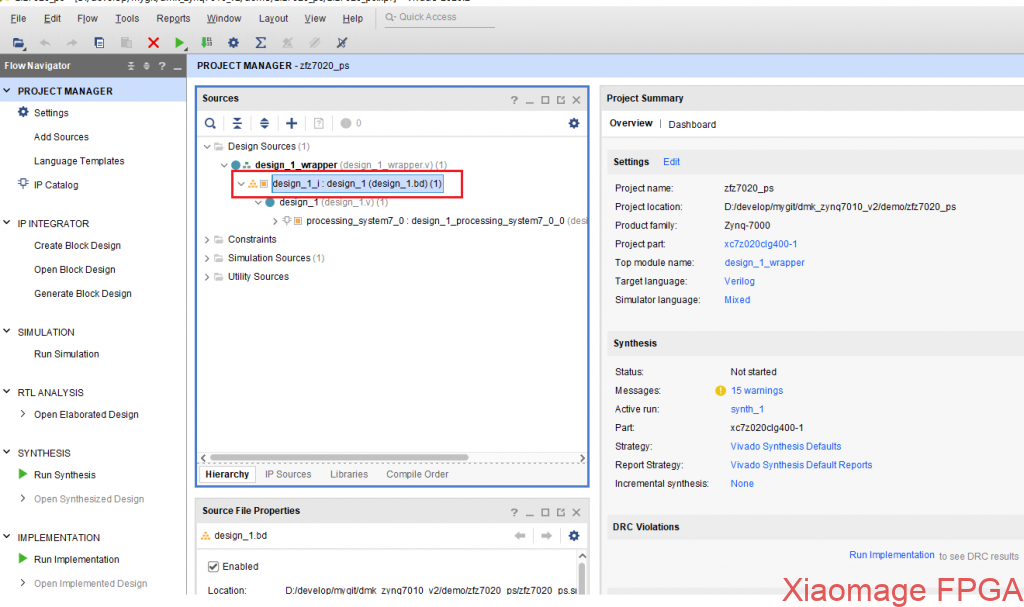

简介 本教程采用官方的lwip库sdk案例实现TCP服务器,并采用iperf.exe测速工具对以太网TCP传输进行测速,实测速度最高可达920MBits/秒。 软件版本 Vivado2020.2+Vitis2020.2。 Vivado工程创建 基于《征服者zynq7020裸机开发教程1--USB Device接口测试(zynq模拟U盘)》的Vivado工程进行微小修改。 1.打开《征服者zynq7020裸机开发教程1--USB Device接口测试(zynq模拟U盘)》的Vivado工程,双…

简介 小马哥FPGA实物成品案例,主要面向有毕业设计、课程设计、科研训练、电子竞赛、项目履历包装等需求的学生客户,包含实物、源码、仿真和售后答疑等。提供了一站式解决方案,到手开箱即用,上电即可出功能,不折腾不闹心。 题目 实物 源码 仿真 论文 FPGA帧差法多运动目标检测(外接VGA显示屏) √ √ √ -- FPGA帧差法多运动目标检测(板载TFTLCD液晶显示屏) √ √ √ -- 基于ZYNQ7020帧差法多运动目标检测(送配套论文) √ √ -- √ FPGA伪彩色处理算法 …

简介 本教程采用官方的usbps库sdk案例,实现zynq模拟U盘,U盘的存储空间由DDR3提供,因此该模拟U盘是掉电数据丢失的。 软件版本 Vivado2020.2+Vitis2020.2。 Vivado工程创建 1.双击打开Vivado软件,点击“Create Project”--点击“Next”; 2.设置工程名和路径 a.在“Project name:”栏填入自定义的Vivado工程名称,注意不能含非英文字符; b.在“Project location:”栏填入(或浏览到)工程想要存放的路径…

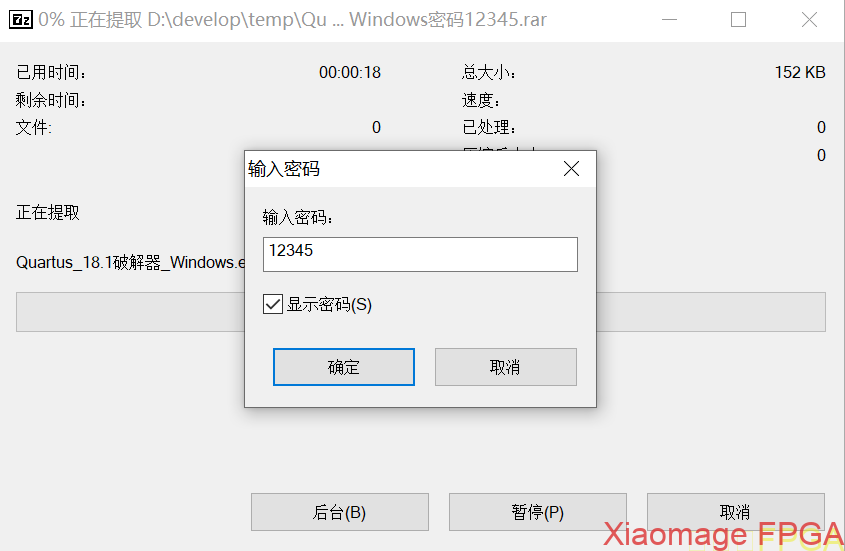

1.下载安装包和破解工具链接 链接:https://pan.baidu.com/s/15j8S7zUYlbJKGxqqySYm-w 提取码:kvwe --来自百度网盘超级会员V9的分享 2.安装Quartusii18.1和Modelsim-ase版本,过程参照教程《FPGA 开发指南.pdf》第二篇软件篇--第四章和第五章 点此下载:《FPGA 开发指南.pdf》 3.破解Quartusii18.1(Modelsim-ase版本不需要破解就可以用) a.解压“Quartus_18.1_破解器_Windows密码…

简介 本案例基于FPGA实现了一个图像自动拍照和UART传输系统,适用于毕业设计、课程设计、科研训练、电子竞赛、项目履历包装等。 项目介绍 硬件平台:小马哥DMK FPGA开发板(含板载TFTLCD液晶显示屏,480*320分辨率) 软件平台:Quartusii18.1(下载、安装和破解教程) 语言 :verilog hdl 功能定义 1.FPGA驱动OV5640摄像头模块采集视频并实时显示在板载TFTLCD显示屏上; 2.每隔N秒,自动保存一张图像数据缓存到SDRAM中,缓存完毕后从S…

项目介绍 硬件平台:DE1-SOC FPGA开发板、LT24液晶屏模块 软件平台:Quartusii18.1(下载、安装和破解教程) 功能定义 功能效果演示 演示视频 发货资料 代码分享 百度网盘:https://pan.baidu.com/s/1TrCOj4i2L1dRD7Cu7iA66g 提取码:6fxi

项目介绍 硬件平台:正点原子新起点FPGA开发板、DS18B20测温芯片 软件平台:Quartusii13.1 语言 :verilog hdl 功能定义 通过DS18B20检测温度并实时显示在数码管上,同时把温度数据实时传输到电脑上位机显示。 功能效果演示 代码分享 点击此处下载

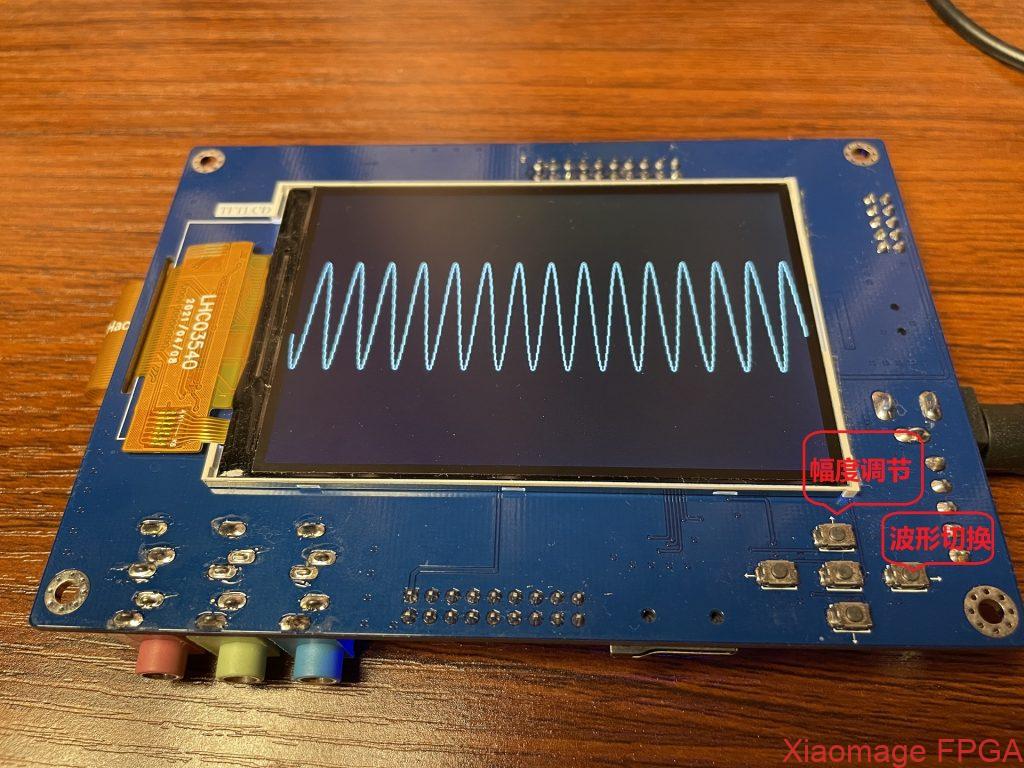

项目介绍 硬件平台:小马哥SA301开发板+黑金AN108 ADDA模块 软件平台:Quartusii13.1 语言 :verilog hdl 功能定义 产生4种波形:正弦波、三角波、锯齿波、方波,并通过DA模块转换成模拟电压波形,可通过示波器查看波形,可通过按键切换波形和调节幅度、频率。 详细要求 产生4种DDS波形:正弦波、三角波、锯齿波、方波; 使用AN108模块转成模拟波形; 通过按键切换四种波形; 通过按键切换幅度和频率; 使用说明 安装说明 AN108模块插在AX40…

项目介绍 硬件平台:小马哥DMK图像处理FPGA开发板 软件平台:Quartusii13.1 语言 :verilog hdl 功能定义 产生4种波形:正弦波、三角波、锯齿波、方波,并显示在TFTLCD显示屏上,可通过按键切换波形和调节幅度。 详细要求 产生4种波形:正弦波、三角波、锯齿波、方波; 在TFTLCD显示屏上显示波形,波形连续不离散; 通过按键切换四种波形; 通过按键切换幅度,至少4种幅度可调; 使用说明 功能效果演示 演示视频 代码分享 [wshop_downloads]

项目介绍 硬件平台:小马哥DMK图像处理FPGA开发板 软件平台:Quartusii13.1 功能定义 基于FPGA的ILI9488 TFTLCD显示屏驱动,Verilog语言源码,实现彩条显示。 详细要求 接口为16bits模式,8080接口; 分辨率480*320; 可任意坐标(x,y)画点; 实现彩条显示; 使用说明 信号 方向 描述 clk12p5M input 同步时钟,最大不超过12.5MHz rst_n input 异步复位,低有效 x[9:0] input 需要画的点的横坐标,范围0~…